# ORGANIZATION OF MICROCOMPUTER

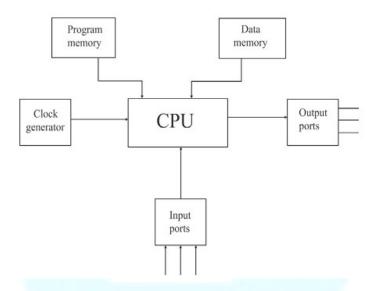

The basic components of a microcomputer are:

- 1) CPU

- 2) Program memory

- 3) Data memory

- 4) Output ports

- 5) Input ports

- 6) Clock generator

These components are shown in figure below:

# 1) Central Processing Unit:

The CPU consists of

- ALU (Arithmetic and Logic Unit)

- Register unit

- Control unit.

The CPU retrieves stored instructions and data word from memory; it also deposits processed data in memory.

### **ALU (Arithmetic and Logic Unit)**

This section performs computing functions on data. These functions are arithmetic operations such as additions subtraction and logical operation such as AND, OR rotate etc. Result are stored either in registers or in memory or sent to output devices.

#### **Register Unit:**

It contains various register. The registers are used primarily to store data temporarily during the execution of a program. Some of the registers are accessible to the uses through instructions.

# **Control Unit:**

It provides necessary timing & control signals necessary to all the operations in the microcomputer. It controls the flow of data between the microprocessor and peripherals (input,

output & memory). The control unit gets a clock which determines the speed of the microprocessors.

The CPU has three basic functions

- 1) It fetches an instructions word stored in memory.

- 2) It determines what the instruction is telling it to do. (Decodes the instruction)

- 3) It executes the instruction.

Executing the instruction may include same of the following major tasks.

- 1. Transfer of data from reg. to reg. in the CPU itself.

- 2. Transfer of data between a CPU reg. & specified memory location.

- 3. Performing arithmetic and logical operations on data from a specific memory location or a designated CPU register.

- 4. Directing the CPU to change a sequence of fetching instruction, if processing the data created a specific condition.

- 5. Performing housekeeping function within the CPU itself in order to establish desired condition at certain registers.

- 4) It looks for control signal such as interrupts and provides appropriate responses.

- 5) It provides states, control, and timing signals that the memory and input/output section can use.

#### 2) Program Memory

The basic task of a microcomputer system into ensure that its CPU executes the desired instruction sequence is the program properly. The instruction sequence is stared in the program memory on initialization- usually a power up and manual reset the processor starts by executing the instruction in a predetermined location in program memory. The first instruction of the program should therefore be in this location in typical µp basic system, the program to be executed is fixed one which does not change. Therefore µp program are store on ROM, or PROM, EPROM, EPROM.

In the trainer kit, ROM contains only the monitor program. The user program is not stored in ROM because it needs not to be stored permanently.

### 3) Data Memory

A microcomputer manipulates data according to the algorithm given by the instruction in the program in the program memory. These instruction may require intermediate results to be stored, the functional block in  $\mu c$  have same internal reg. which can also be used if available for such storage external data memory is needed if the storage requirements is more.

Apart from intermediate storage, the data memory may also be used to provide data needed by the program, to store some of the results of the program. Data memory is used for all storage purposes other than storage of program. Therefore, they must have head write capability RWM or RAM.

It stores both the instructions to be executed (i.e. program) and the data involved. It usually contains ROM (Read memory). The ROM can only read and cannot be written into and is non volatile that is, it retains its contents when the power is turned off. A ROM is typically used to store instructions and data that do not change. For example, it stores the monitor program if a microcomputer.

One can either read from or write into a RWM. The RWM is volatile, that is it does not retain its contents when the power is turned off. It is used to store user programmes & data which are

temporary might change during the course of executing a program. Both ROM & RWM are RAM (Random access memory). RWM is respectively.

During a memory read operation, the content of the addressed location is not destroyed. During a unit operation, the original content of the addressed location is destroyed.

Both ROM & RWM are arranged into words, each of which has a unique address. The address of a word is memory location and it is placed in parentheses. Therefore, X is an address and (X) is the content of that address X.

The address decodes taken an address and from the control unit and select the proper memory location and obtaining its content takes a certain amount of time, this times is the access time of the memory. The access time affects the speed of the computer, pins, and the computer must obtain the instruction and data from the memory. Computer memory as usually RAM so that all memory location have the same access time. The computer must wait shiner of unit's memory, typical memory access time range from several uses. Memory sections often subdivided into units called pages. The entire memory section may involve million of cords, when a page contains between 256 & 4k warts. The computer may access a memory location by first decreasing a particular page and then accessing a location on that page. The advantage of paging is that the computer can reach several locations on the same page with just the address in the page. The process is like describing street address by first specifying aspect and them listing the have numbers. The control section transfers data to or from memory as follows.

- 1. The control section reads an address to the memory.

- 2. The control section sends a read and write signal to the memory to indicate, the direction of the transform.

- 3. The control section waits until transfer has been completed .this delay precedes the actual data's transfer in the input case and follows it in the output case.

### 4) Input/ Output Ports:

The input & output ports provide the microcomputer the capability to communicate with the outside world. The input ports allow data to pass from the outside world to the  $\mu c$  data which will be used in the data manipulation being done by the microcomputer to send data to output devices

The user can enter instruction (i.e. program) and data in memory through input devices such as keyboard, or simple switches, CRT, disk devices, tape or card readers. Computers are also used to measure and control physical quantities like temperature, pressure, speed etc. For these purposes, transducers are used to convent physical quantise into proportional electrical signals A/D computers are used to convert electrical signals into digital signals which are sent to the compute. The computer sends the results of the computation to the output devices e.g. LED, CRT, D/A converters, printers etc. These I/O devices allow the computer to communicate with the outside world I/O devices are called peripherals.

#### 5) Clock Generator:

Operations inside the p as well as in other parts of the c are usually synchronous by nature. The clock generator generates the appropriate clock periods during which instruction executions are carried out by the microprocessor. This condition ensures that events in different path of the systems can proceed in a systematic fashion.

Some of the microprocessors have an internal clock generator circuit to generate a clock signal. These microprocessors require an external crystal or RC network to be connected at the appropriate pins for deciding the operating frequency (e.g. 8085). Some microprocessors require an external clock generator (e.g. 8086). These microprocessors also provides an output clock signal which can be used by other devices in the microcomputer system for their can timing and synchronizing.

# **MICROPROCESSOR AS CPU**

- CPUs and microprocessors are the bread and butter of a successful operating system.

- They both execute integral computer tasks, such as arithmetic, data processing, logic and I/O operations, but CPU vs. microprocessor differences aren't all so black and white.

- Though some IT administrators use CPU and microprocessor interchangeably, the reality is that most CPUs are microprocessors but not every microprocessor is a CPU.

#### What is a CPU?

- A processor, or CPU, is logic circuitry that responds and processes basic instructions to drive a computer.

- A CPU is integral to system operations because it's responsible for interpreting a majority of a computer's commands, such as basic arithmetic, logic and I/O processes.

- A CPU can also allocate commands at will for other chips and components within a system.

- Various elements within the CPU enable it to execute these computer commands, such as the arithmetic logic unit, floating point unit, registers, and L1 and L2 cache memory.

- With the help of these components, a CPU can fulfil functions such as fetch, decode and execute. In this three-part function, the fetch step receives program memory instructions from a system's RAM, the decode step converts the instructions to understand which parts of the CPU are required to continue operations and the execute step performs the operation.

- Most CPUs in modern IT are multicore processors, which means the integrated circuitry has two or more processors attached to help improve performance, reduce power consumption and support simultaneous processing of several computer tasks. Generally speaking, a multicore CPU is twice as powerful as a single core CPU.

#### What is a microprocessor?

- On the other hand, a microprocessor -- also known as a logic chip -- is essentially a single-chip implementation of a CPU.

- A microprocessor contains all of a CPU's functions and can perform arithmetic and logic operations with registers.

- However, a microprocessor's functions differ in some ways to a CPU.

- For example, a microprocessor can add, subtract, compare and fetch numbers within a system from one area to another.

- When admins turn on a computer, the microprocessor receives the first instruction from the BIOS.

- From there, the microprocessor either receives further instruction from the BIOS, the OS the BIOS loads into the computer memory or an application that drives the microprocessor.

- In modern IT, a majority of CPUs tend to be microprocessors by default because of their ability to execute data movement, perform complex calculations and increase speed within a system.

- The two main microprocessor vendors that garner significant popularity are Intel and Advanced Micro Devices.

- Other microprocessors on the market include ARM, Sparc and PowerPC.

# DIFFERENCE BETWEEN CPU AND MICROPROCESSOR

- Central processing unit (CPU) is the hardware within a computer system that carries out the instructions of a computer program by performing the basic arithmetical, logical, and input/output operations of the system.

- It is also called a central processor unit, or more commonly a processor.

- However, many mistakenly use the term CPU to refer to the housing unit that stores all of the computer's hardware, whereas, in actuality it is just the small processor chip that runs the computer's programs.

- The CPU is housed in a single silicon chip called a microprocessor.

- The fundamental function of a CPU is to run or execute a program. A program is essentially a sequence of stored instructions, which is represented by a series of numbers that are kept in some kind of computer memory.

- CPUs follow a four step process in their operation: fetch, decode, execute, and write back.

- A microprocessor incorporates all of the functions of a computer's CPU on a single integrated circuit (IC).

- Initially, it required more than one circuit in order to house the CPU, as the technology became more advanced, the need for that many circuits reduced.

- Today a microprocessor can house around 4 CPUs for quad-core technologies.

- In addition to the CPU, the microprocessor also packs I/O and memory access circuits.

- It is a programmable device that receives data, processes it according to stored directions and then gives results in the form of output.

- The primary language is binary code, a system of 1 and 0s.

- Microprocessors are responsible for controlling the logic of almost all digital devices.

- The internal working of a microprocessor depends on the design and purpose of the microprocessor. It is limited by number of transistors that can be placed on the chip, the number of package terminations that can connect the processor to the other parts of the computer, the number of interconnections possible and the amount of heat that the chip generates.

- In short, the microprocessor is a set of circuits that connect the rest of the computer to the CPU, allowing the system to execute directions.

• Many microprocessors also exist without CPUs attached to it.

Due to the similarity in usage, it is easy to understand why both of these words have become synonymous. If a person were to refer to a microprocessor as a CPU and vice-versa, it would be acceptable.

# 8085 PROGRAM FOR ADDITION OF TWO 8 BITS

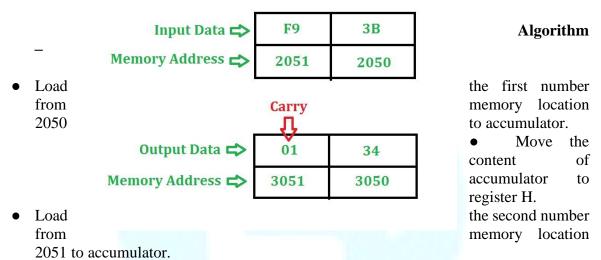

An assembly language program to add two 8 bit numbers stored at address 2050 and address 2051 in 8085 microprocessor. The starting address of the program is taken as 2000.

# Example -

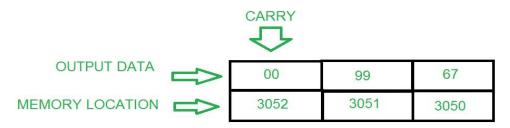

- Then add the content of register H and accumulator using "ADD" instruction and storing result at 3050

- The carry generated is recovered using "ADC" command and is stored at memory location 3051

### Program -

| Memory Address | <b>Mnemonics</b> | Comment                      |

|----------------|------------------|------------------------------|

| 2000           | LDA 2050         | A<-[2050]                    |

| 2003           | MOV H, A         | H<-A                         |

| 2004           | LDA 2051         | A < -[2051]                  |

| 2007           | ADD H            | A < -A + H                   |

| 2008           | MOV L, A         | L←A                          |

| 2009           | MVI A 00         | A←00                         |

| 200B           | ADC A            | $A \leftarrow A + A + carry$ |

| 200C           | MOV H, A         | Н←А                          |

| 200D           | SHLD 3050        | $H\to 3051, L\to 3050$       |

| 2010           | HLT              |                              |

#### Explanation –

- LDA 2050 moves the contents of 2050 memory location to the accumulator.

- MOV H, A copies contents of Accumulator to register H to A

- LDA 2051 moves the contents of 2051 memory location to the accumulator.

- ADD H adds contents of A (Accumulator) and H register (F9). The result is stored in A itself. For all arithmetic instructions A is by default an operand and A stores the result as well.

- MOV L, A copies contents of A (34) to L

- MVI A 00 moves immediate data (i.e., 00) to A

- ADC A adds contents of A (00), contents of register specified (i.e. A) and carry (1). As ADC is also an arithmetic operation, A is by default an operand and A stores the result as well.

- MOV H, A copies contents of A (01) to H

- SHLD 3050 moves the contents of L register (34) in 3050 memory location and contents of H register (01) in 3051 memory location

- HLT stops executing the program and halts any further execution

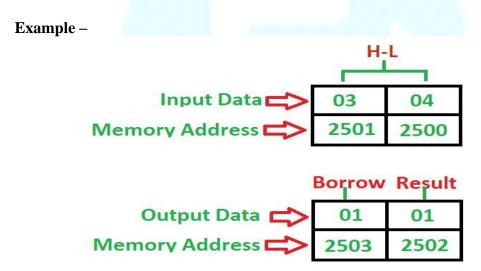

# 8085 PROGRAM FOR SUBTRACTION OF TWO 8 BITS NUMBERS

An assembly language program to subtract two 8-bit numbers with or without borrow where first number is at 2500 memory address and second number is at 2501 memory address and store the result into 2502 and borrow into 2503 memory address.

## Algorithm -

- Load 00 in a register C (for borrow)

- Load two 8-bit number from memory into registers

- Move one number to accumulator

- Subtract the second number with accumulator

- If borrow is not equal to 1, go to step 7

- Increment register for borrow by 1

- Store accumulator content in memory

- Move content of register into accumulator

- Store content of accumulator in other memory location

Stop

# Program -

| Memory | <b>Mnemonics</b> | <b>Operands</b> | Comment                           |

|--------|------------------|-----------------|-----------------------------------|

| 2000   | MVI              | C, 00           | [C] <- 00                         |

| 2002   | LHLD             | 2500            | [H-L] <- [2500]                   |

| 2005   | MOV              | A, H            | [A] <- [H]                        |

| 2006   | SUB              | L               | [A] < -[A] - [L]                  |

| 2007   | JNC              | 200B            | Jump If no borrow                 |

| 200A   | INR              | C               | [C] < -[C] + 1                    |

| 200B   | STA              | 2502            | $[A] \rightarrow [2502]$ , Result |

| 200E   | MOV              | A, C            | [A] <- [C]                        |

| 2010   | STA              | 2503            | [A] -> [2503], Borrow             |

| 2013   | HLT              |                 | Stop                              |

# Explanation – Registers A, H, L, C are used for general purpose:

- MOV is used to transfer the data from memory to accumulator (1 Byte)

- LHLD is used to load register pair directly using 16-bit address (3 Byte instruction)

- MVI is used to move data immediately into any of registers (2 Byte)

- STA is used to store the content of accumulator into memory(3 Byte instruction)

- INR is used to increase register by 1 (1 Byte instruction)

- JNC is used to jump if no borrow (3 Byte instruction)

- SUB is used to subtract two numbers where one number is in accumulator(1 Byte)

- HLT is used to halt the program.

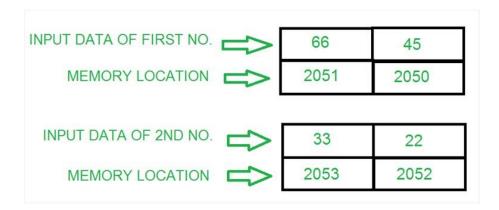

# 8085 PROGRAM TO ADD TWO 16 BIT NUMBERS

An assembly language program to add two 16 bit numbers by using:

- 1. 8-bit operation

- 2. 16-bit operation

# Example -

# 1. Addition of 16-bit numbers using 8-bit operation:

It is a lengthy method and requires more memory as compared to the 16-bit operation.

# Algorithm:

- Load the lower part of the first number in the B register.

- Load the lower part of the second number in A (accumulator).

- Add both the numbers and store.

- Load the higher part of the first number in the B register.

- Load the higher part of the second number in A (accumulator).

- Add both the numbers with carrying from the lower bytes (if any) and store them at the next location.

### **Program:**

| MEMORY ADDRESS | <b>MNEMONICS</b> | COMMENTS                  |

|----------------|------------------|---------------------------|

| 2000           | LDA 2050         | $A \leftarrow 2050$       |

| 2003           | MOV B, A         | $B \leftarrow A$          |

| 2004           | LDA 2052         | $A \leftarrow 2052$       |

| 2007           | ADD B            | $A \leftarrow A + B$      |

| 2008           | STA 3050         | $A \rightarrow 3050$      |

| 200B           | LDA 2051         | $A \leftarrow 2051$       |

| 200E           | MOV B, A         | $B \leftarrow A$          |

| 200F           | LDA 2053         | $A \leftarrow 2053$       |

| 2012           | ADC B            | $A \leftarrow A + B + CY$ |

| 2013           | STA 3051         | $A \rightarrow 3051$      |

| 2016           | HLT              | Stops execution           |

### **Explanation:**

- LDA 2050 stores the value at 2050 in A (accumulator).

- MOV B, A stores the values of A into the B register.

- LDA 2052 stores the value at 2052 in A.

- ADD B add the contents of B and A and store them in A.

- STA 3050 stores the result in memory location 3050.

- LDA 2051 stores the value at 2051 in A.

- MOV B, A stores the values of A into the B register.

- LDA 2053 stores the value at 2053 in A.

- ADC B adds the contents of B, A, and carry from the lower bit addition and store in A.

- STA 3051 stores the result in memory location 3051.

• HLT stops execution.

# 2. Addition of 16 bit numbers using 16-bit operation:

It is a very short method and less memory is also required as compared to 8-bit operations.

### Algorithm:

- Load both the lower and the higher bits of the first number at once.

- Copy the first number to another registered pair.

- Load both the lower and the higher bits of second number at once.

- Add both the register pairs and store the result in a memory location.

# **Program:**

| MEMORY ADDRESS | <b>MNEMONICS</b> | COMMENTS                                   |   |

|----------------|------------------|--------------------------------------------|---|

| 2000           | LHLD 2050        | H-L ← 2050                                 |   |

| 2003           | XCHG D           | \leftrightarrow H & E \leftrightarrow      | L |

| 2004           | LHLD 2052        | H-L ← 2052                                 |   |

| 2007           | DAD D            | $H \leftarrow H + D \& L \leftarrow L + E$ |   |

| 2008           | SHLD 3050        | $L \to 3050 \& H \to 3051$                 |   |

| 200B           | HLT              | Stops execution                            |   |

# **Explanation:**

- LHLD 2050 loads the value at 2050 in L register and that in 2051 in the H register (first number)

- XCHG copies the content of the H to D register and L to E register

- LHLD 2052 loads the value at 2052 in L register and that in 2053 in the H register (second number)

- DAD D adds the value of H with D and L with E and stores the result in H and L

- SHLD 3050 stores the result at memory location 3050

- HLT stops execution

# 8085 PROGRAM TO SUBTRACT TWO 16 BIT NUMBERS

An assembly language program in 8085 microprocessor to subtract two 16 bit numbers.

# Assumption -

Starting address of program: 2000

Input memory location: 2050, 2051, 2052, 2053

Output memory location: 2054, 2055

# Algorithm -

- Get the LSB in L register and MSB in H register of 16 Bit number.

- Exchange the content of HL register with DE register.

- Again Get the LSB in L register and MSB in H register of 16 Bit number.

- Subtract the content of L register from the content of E register.

- Subtract the content of H register from the content of D register and borrow from previous step.

- Store the result in memory location.

#### Program -

| MEMORY ADDRESS | <b>MNEMONICS</b> | COMMENTS                        |

|----------------|------------------|---------------------------------|

| 2000           | LHLD 2050        | Load H-L pair with address 2050 |

| 2003           | XCHG             | EXCHANGE H-L PAIR WITH D-E PAIR |

| 2004           | LHLD 2052        | Load H-L pair with address 2052 |

| 2007           | MVI C, 00        | C<-00H                          |

| 2009           | MOV A, E         | A<-E                            |

| 200A           | SUB L            | A<-A-L                          |

| 200B           | STA 2054         | 2054<-A                         |

| 200E           | MOV A, D         | A<-D                            |

| 200F           | SBB H            | SUBTRACT WITH BORROW            |

| 2010           | STA 2055         | 2055<-A                         |

| 2013           | HLT              | TERMINATES THE PROGRAM          |

## Explanation -

- LHLD 2050: load HL pair with address 2050.

- XCHG: exchange the content of HL pair with DE.

- LHLD 2052: load HL pair with address 2050.

- MOV A, E: move the content of register E to A.

- SUB L: subtract the content of A with the content of register L.

- STA 2054: store the result from accumulator to memory address 2054.

- MOV A, D: move the content of register D to A.

- SBB H: subtract the content of A with the content of register H with borrow.

- STA 2055: store the result from accumulator to memory address 2055.

- HLT: stops executing the program and halts any further execution.

# 8085 MICROPROCESSOR

- 8085 is an 8-bit microprocessor as it operates on 8 bits at a time designed by Intel in 1977 using NMOS technology.

- This microprocessor exhibits some unique characteristics and this is the reason it still holds popularity among the microprocessors.

- Basically, 8085 was the first commercially successful microprocessor by Intel.

- As some of the architectural drawbacks associated with 8080 was also eliminated by 8085.

- 8085 is pronounced as "eighty-eighty-five" microprocessor. It has the following configuration

- 8-bit data bus

- 16-bit address bus, which can address up to 64KB

- A 16-bit program counter

- A 16-bit stack pointer

- Six 8-bit registers arranged in pairs: BC, DE, HL

- Requires +5V supply to operate at 3.2 MHZ single phase clock

- It is used in washing machines, microwave ovens, mobile phones, etc.

## FEATURES OF 8085

- 1. It is an 8-bit microprocessor i.e. it can accept, process, or provide 8-bit data simultaneously.

- 2. It operates on a single +5V power supply connected at Vcc; power supply ground is connected to Vss.

- 3. It operates on clock cycle with 50% duty cycle.

- 4. It has on chip clock generator. This internal clock generator requires tuned circuit like LC, RC or crystal. The internal clock generator divides oscillator frequency by 2 and generates clock signal, which can be used for synchronizing external devices.

- 5. It can operate with a 3 MHz clock frequency. The 8085A-2 version can operate at the maximum frequency of 5 MHz

- 6. It has 16 address lines, hence it can access (216) 64 Kbytes of memory.

- 7. It provides 8 bit I/O addresses to access (2<sup>8</sup>) 256 I/O ports.

- 8. In 8085, the lower 8-bit address bus (A0 A7) and data bus (D0 D7) are Multiplexed to reduce number of external pins. But due to this, external hardware (latch) is required to separate address lines and data lines.

- 9. It supports 74 instructions with the following addressing modes:

- Immediate

- Register

- Direct

- Indirect

- Implied

- 10. The Arithmetic Logic Unit (ALU) of 8085 performs:

- 8 bit binary addition with or without carry

- 16 bit binary addition

- 2 digit BCD addition.

- 8-bit binary subtraction with or without borrow

- 8-bit logical AND, OR, EX-OR, complement (NOT), and bit shift operations.

- 11. It has 8-bit accumulator, flag register, instruction register, six 8-bit general purpose registers (B, C, D, E, H and L) and two 16-bit registers. (SP and PC). Getting the operand from the general purpose registers is faster than from memory. Hence skilled programmers always prefer general purpose registers to store program variables than memory.

- 12. It provides five hardware interrupts: TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR.

- 13. It has serial I/O control which allows serial communication.

- 14. It provides control signals (IO/M, RD, WR) to control the bus cycles, and hence external bus controller is not required.

- 15. The external hardware (another microprocessor or equivalent master) can detect which machine cycle microprocessor is executing using status signals (IO/M, S<sub>0</sub>, S<sub>1</sub>). This feature of 8085 Microprocessor is very useful when more than one processor is using common system resources (memory and I/O devices).

- 16. It has a mechanism by which it is possible to increase its interrupt handling capacity.

- 17. The 8085 has an ability to share system bus with Direct Memory Access controller. This Features of 8085 Microprocessor allows to transfer large amount of data from I/O device to memory or from memory to I/O device with high speeds.

- 18. Features of 8085 Microprocessor can be used to implement three chip microcomputer with supporting I/O devices like IC 8155 and IC 8355.

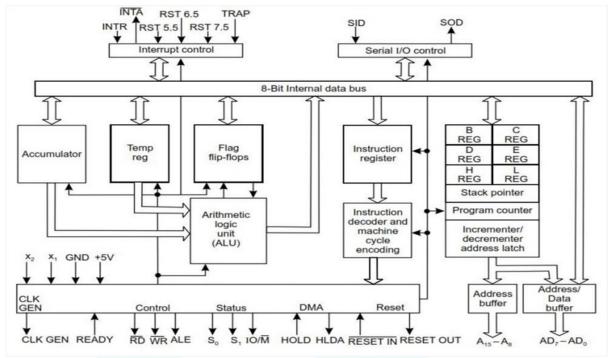

# **ARCHITECTURE OF 8085**

8085 is an 8-bit, general-purpose microprocessor. It consists of the following functional units:

#### Accumulator

It is an 8-bit register used to perform arithmetic, logical, I/O & LOAD/STORE operations. It is connected to internal data bus & ALU.

## Arithmetic and logic unit

As the name suggests, it performs arithmetic and logical operations like Addition, Subtraction, AND, OR, etc. on 8-bit data.

#### General purpose register

There are 6 general purpose registers in 8085 processor, i.e. B, C, D, E, H & L. Each register can hold 8-bit data.

These registers can work in pair to hold 16-bit data and their pairing combination is like B-C, D-E & H-L.

### **Program counter**

It is a 16-bit register used to store the memory address location of the next instruction to be executed. Microprocessor increments the program whenever an instruction is being executed, so that the program counter points to the memory address of the next instruction that is going to be executed.

#### Stack pointer

It is also a 16-bit register works like stack, which is always incremented/decremented by 2 during push & pop operations.

### **Temporary register**

It is an 8-bit register, which holds the temporary data of arithmetic and logical operations.

#### Flag register

It is an 8-bit register having five 1-bit flip-flops, which holds either 0 or 1 depending upon the result stored in the accumulator.

These are the set of 5 flip-flops –

- Sign (S)

- Zero (Z)

- Auxiliary Carry (AC)

- Parity (P)

- Carry (C)

- Its bit position is shown in the following table –

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| S  | Z  |    | AC |    | P  |    | CY |

|    |    |    |    |    |    |    |    |

# Instruction register and decoder

It is an 8-bit register. When an instruction is fetched from memory then it is stored in the Instruction register. Instruction decoder decodes the information present in the Instruction register.

### Timing and control unit

It provides timing and control signal to the microprocessor to perform operations. Following are the timing and control signals, which control external and internal circuits –

• Control Signals: READY, RD', WR', ALE

Status Signals: S0, S1, IO/M'DMA Signals: HOLD, HLDA

• RESET Signals: RESET IN, RESET OUT

#### **Interrupt control**

As the name suggests it controls the interrupts during a process. When a microprocessor is executing a main program and whenever an interrupt occurs, the microprocessor shifts the control from the main program to process the incoming request. After the request is completed, the control goes back to the main program.

There are 5 interrupt signals in 8085 microprocessor: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP.

### **Serial Input/output control**

It controls the serial data communication by using these two instructions: SID (Serial input data) and SOD (Serial output data).

#### Address buffer and address-data buffer

The content stored in the stack pointer and program counter is loaded into the address buffer and address-data buffer to communicate with the CPU. The memory and I/O chips are connected to these buses; the CPU can exchange the desired data with the memory and I/O chips.

# Address bus and data bus

Data bus carries the data to be stored. It is bidirectional, whereas address bus carries the location to where it should be stored and it is unidirectional. It is used to transfer the data & Address I/O devices.

**ARCHITECTURE OF 8085**

# **TIMINGS OF INTEL 8085**

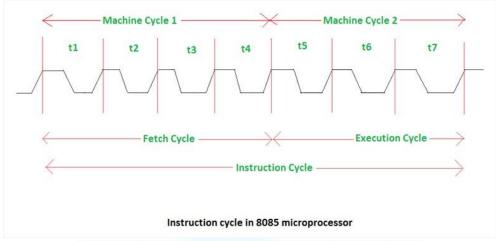

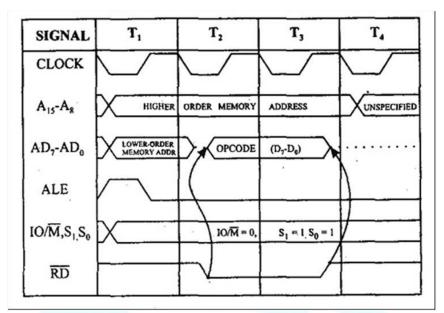

Timing Diagram is a graphical representation. It represents the execution time taken by each instruction in a graphical format. The execution time is represented in T-states.

# **INSTRUCTION CYCLE**

Time required to execute and fetch an entire instruction is called instruction cycle. It consists:

- **Fetch cycle** The next instruction is fetched by the address stored in program counter (PC) and then stored in the instruction register.

- **Decode instruction** Decoder interprets the encoded instruction from instruction register.

- Reading effective address The address given in instruction is read from main memory and required data is fetched. The effective address depends on direct addressing mode or indirect addressing mode.

- Execution cycle consists memory read (MR), memory write (MW), input output read (IOR) and input output write (IOW)

# **MACHINE CYCLE**

- The time required by the microprocessor to complete an operation of accessing memory or input/output devices is called machine cycle.

- One time period of frequency of microprocessor is called t-state.

- A t-state is measured from the falling edge of one clock pulse to the falling edge of the next clock pulse.

- Fetch cycle takes four t-states and execution cycle takes three t-states.

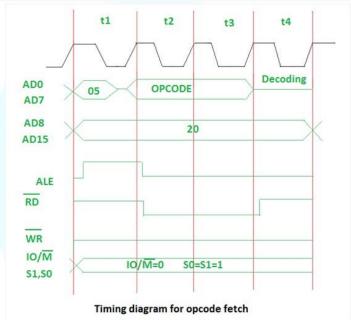

### Above diagram represents:

- 05 Lower bit of address where opcode is stored. Multiplexed address and data bus AD0-AD7 are used.

- 20 Higher bit of address where opcode is stored. Multiplexed address and data bus AD8-AD15 are used.

- ALE Provides signal for multiplexed address and data bus. If signal is high or 1, multiplexed address and data bus will be used as address bus. To fetch lower bit of address, signal is 1 so that multiplexed bus can act as address bus. If signal is low or 0, multiplexed bus will be used as data bus. When lower bit of address is fetched then it will act as data bus as the signal is low.

- RD (low active) If signal is high or 1, no data is read by microprocessor. If signal is low or 0, data is read by microprocessor.

- WR (low active) If signal is high or 1, no data is written by microprocessor. If signal is low or 0, data is written by microprocessor.

- IO/M (low active) and S1, S0 If signal is high or 1, operation is performing on input output. If signal is low or 0, operation is performing on memory

| Machine Cycle            | Status |    |    | Contr | ol Signal | s    |

|--------------------------|--------|----|----|-------|-----------|------|

|                          | 10/M   | S1 | so | RD    | WR        | INTA |

| Opcode Fetch             | 0      | 1  | 1  | 0     | 1         | 1    |

| Memory Read              | 0      | 1  | 0  | 0     | 1         | 1    |

| Memory Write             | 0      | 0  | 1  | 1     | 0         | 1    |

| I/O Read                 | 1      | 1  | 0  | 0     | 1         | 1    |

| I/O Write                | 1      | 0  | 1  | 1     | 0         | 1    |

| Interrupt<br>Acknowledge | 1      | 1  | 1  | 1     | 1         | 0    |

| HALT                     | Z      | 0  | 0  | Z     | Z         | 1    |

| HOLD                     | Z      | X  | X  | Z     | Z         | 1    |

| RESET                    | Z      | X  | X  | Z     | Z         | 1    |

Where Z is tri state (pin neither connected to supply nor ground. High impedance) and X represents do not care.

#### 8085 machine cycle status and control signals

- The following are the various machine cycles of 8085 microprocessor.

- 1. Opcode Fetch (OF)

- 2. Memory Read (MR)

- 3. Memory Write (MW)

- 4. I/O Read (IOR)

- 5. I/O Write (IOW)

- 6. Interrupt Acknowledge (IA)

- 7. Bus Idle (BI)

- All instructions have at least one Opcode Fetch machine cycle.

- Depending on the type of instruction one or more other machine cycles are required to complete the execution of the instruction.

### **Opcode Fetch (OF) machine cycle of 8085:**

- Each instruction of the microprocessor has one byte Opcode.

- The Opcode is stored in memory.

- In order to fetch the Opcode from memory, processor executes the Opcode Fetch machine cycle.

- So, every instruction starts with Opcode Fetch machine (OFM) cycle.

- The time taken by the microprocessor to execute the Opcode Fetch cycle is4T (T-states).

- In order to fetch the Opcode from memory, the first 3 T-states are used.

- The remaining T-state is used for internal operations by the microprocessor.

The timing diagram for Opcode Fetch machine cycle is shown in figure.

The steps in Opcode Fetch machine cycle are given in table.

| S. No | T state | Operation                                                                                                                                                                         |

|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | T1      | The microprocessor places the higher order 8-bits of the memory address on A15 – A8 address bus and the lower order 8-bits of the memory address on AD7 – AD0 address / data bus. |

| 2     |         | The microprocessor makes the ALE signal HIGH and at the middle of T1 state, ALE signal goes LOW.                                                                                  |

| 3     |         | The status signals are changed as IO/M' = 0, S1 =1 and S0 = 1.  These status signals do not change throughout the OF machine cycle.                                               |

| 4 | Т2 | The microprocessor makes the RD' line LOW to enable memory read and increments the Program Counter. |

|---|----|-----------------------------------------------------------------------------------------------------|

| 5 |    | The contents on D7 – D0<br>(i.e. the Opcode) are<br>placed on the<br>address / data bus.            |

| 6 | Т3 | The microprocessor transfers the Opcode on the address / data bus to Instruction Register (IR).     |

| 7 |    | The microprocessor makes the RD' line HIGH to disable memory read.                                  |

| 8 | T4 | The microprocessor decodes the instruction.                                                         |

# **Memory Read Machine Cycle of 8085:**

- Single byte instructions require only Opcode Fetch machine cycles.

- But, 2-byte and 3-byte instructions require additional machine cycles to read the operands from memory.

- The additional machine cycle is called Memory Read machine cycle.

- For example, the instruction MVI A, 50H requires one OF machine cycle to fetch the operand from memory and one MR machine cycle to read the operand (50H) from memory.

- The MR machine cycle takes 3 T-states.

The timing diagram for Memory Read machine cycle is shown in figure.

| SIGNAL                              | T <sub>1</sub>             | T,                                | T,                                |

|-------------------------------------|----------------------------|-----------------------------------|-----------------------------------|

| CLOCK                               |                            |                                   |                                   |

| A <sub>15</sub> -A <sub>8</sub>     | HIGHER                     | ORDER MEMORY                      | ADDRESS                           |

| AD <sub>7</sub> -AD <sub>0</sub>    | LOWER-ORDER<br>MEMORY ADDR | DATA                              | (D <sub>7</sub> -D <sub>6</sub> ) |

| ALE                                 |                            |                                   | 1                                 |

| IO/M,S <sub>1,</sub> S <sub>0</sub> | X                          | $10\sqrt{M} = 0, \qquad S_1 = 1.$ | S <sub>0</sub> = 0                |

| RD                                  |                            | 1                                 |                                   |

The steps in Memory Read machine cycle are given in table.

| The microprocessor places the address of the I/O port specified in the instruction or A15 – A8 address bus and also on AD7 – AD0 address / data bus.  The microprocessor makes the ALE signal HIGH and at the middle of T1 state ALE signal goes LOW. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| the I/O port specified in the instruction or A15 – A8 address bus and also on AD7 – AD0 address / data bus.  The microprocessor makes the ALE signal HIGH and at the middle of T1 state. ALE signal goes                                              |

| in the instruction or A15 – A8 address bus and also on AD7 – AD0 address / data bus.  2  The microprocessor makes the ALE signal HIGH and at the middle of T1 state ALE signal goes                                                                   |

| A15 – A8 address bus and also on AD7 – AD0 address / data bus.  2 The microprocessor makes the ALE signal HIGH and at the middle of T1 state. ALE signal goes                                                                                         |

| and also on AD7 – AD0 address / data bus.  The microprocessor makes the ALE signal HIGH and at the middle of T1 state ALE signal goes                                                                                                                 |

| AD0 address / data bus.  The microprocessor makes the ALE signal HIGH and at the middle of T1 state. ALE signal goes                                                                                                                                  |

| bus.  The microprocessor makes the ALE signal HIGH and at the middle of T1 state.  ALE signal goes                                                                                                                                                    |

| The microprocessor makes the ALE signal HIGH and at the middle of T1 state.  ALE signal goes                                                                                                                                                          |

| makes the ALE signal HIGH and at the middle of T1 state. ALE signal goes                                                                                                                                                                              |

| HIGH and at the middle of T1 state.  ALE signal goes                                                                                                                                                                                                  |

| middle of T1 state. ALE signal goes                                                                                                                                                                                                                   |

| ALE signal goes                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                       |

| LOW.                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                       |

| The status signals are                                                                                                                                                                                                                                |

| changed as $IO/M' = 0$                                                                                                                                                                                                                                |

| S1 = 1 and $S0 = 0$                                                                                                                                                                                                                                   |

| These status signals                                                                                                                                                                                                                                  |

| do not change                                                                                                                                                                                                                                         |

| throughout the I/C                                                                                                                                                                                                                                    |

| 4 T2 read machine cycle.  The microprocessor                                                                                                                                                                                                          |

| T2 The microprocessor makes the RD' line                                                                                                                                                                                                              |

| LOW to enable I/O                                                                                                                                                                                                                                     |

| read.                                                                                                                                                                                                                                                 |

| 5 The contents on D7 – D0                                                                                                                                                                                                                             |

| (i.e. the data) are                                                                                                                                                                                                                                   |

| placed on the address                                                                                                                                                                                                                                 |

| data bus.                                                                                                                                                                                                                                             |

| 6 T3 The data loaded on the                                                                                                                                                                                                                           |

| address / data bus is                                                                                                                                                                                                                                 |

| moved to the                                                                                                                                                                                                                                          |

|     | microprocessor i.e., to the accumulator. |

|-----|------------------------------------------|

| 7 . | The microprocessor                       |

|     | makes the RD' line                       |

|     | HIGH to disable the                      |

|     | I/O read operation                       |

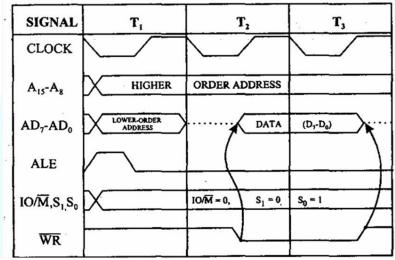

# **Memory Write Machine Cycle of 8085:**

- Microprocessor uses the Memory Write machine cycle for sending the data in one of the registers to memory.

- For example, the instruction STA 5000H writes the data in accumulator to the memory location 5000H. The MW machine cycle takes 3 T-states.

The timing diagram for Memory Write machine cycle is shown in figure.

The steps to disable the memory write machine cycle are given in table.

| S. No | T state | Operation                |

|-------|---------|--------------------------|

| 1     | T1      | The microprocessor       |

|       |         | places the higher order  |

|       |         | 8-bits of the memory     |

|       |         | address on A15 – A8      |

|       |         | address bus and the      |

|       |         | lower order 8-bits of    |

|       |         | the memory address       |

|       |         | on AD7 – AD0             |

|       |         | address / data bus.      |

| 2     |         | The microprocessor       |

|       |         | makes the ALE signal     |

|       |         | HIGH and at the          |

|       |         | middle of T1 state,      |

|       |         | ALE signal goes          |

|       |         | LOW.                     |

| 3     |         | The status signals are   |

|       |         | changed as $IO/M' = 0$ , |

|     |    | S1 =0 and S0 = 1.<br>These status signals |

|-----|----|-------------------------------------------|

|     |    | do not change                             |

|     |    | throughout the                            |

|     |    | memory write                              |

|     |    | machine cycle.                            |

| 4   | T2 | The microprocessor                        |

|     |    | makes the $WR$ ' lines                    |

|     |    | LOW to enable                             |

|     |    | memory write.                             |

| 5   |    | The contents of the                       |

|     |    | specified register are                    |

|     |    | placed on the address /                   |

|     |    | data bus.                                 |

| 6   | T3 | The data placed on the                    |

|     |    | address / data bus is                     |

|     |    | transferred to the                        |

|     |    | specified memory                          |

|     |    | location.                                 |

| 7 . |    | The microprocessor                        |

|     |    | makes the $\overline{WR}$ ' line          |

|     |    | HIGH to disable the                       |

|     |    | memory write                              |

|     |    | operation                                 |

# I/O Read Machine Cycle of 8085

- Microprocessor uses the I/O Read machine cycle for receiving a data byte from the I/O port or from the peripheral in I/O mapped I/O systems.

- The IN instruction uses this machine cycle during execution.

- The IOR machine cycle takes 3 T-states.

The timing diagram for I/O Read machine cycle is shown in figure.

| SIGNAL    | T <sub>1</sub> | T <sub>2</sub>     | Т,                                    |          |

|-----------|----------------|--------------------|---------------------------------------|----------|

| CLOCK     |                |                    |                                       |          |

| A15-A8    | X              | I/O Port address   | s                                     |          |

| AD,-ADe   | I/O Port addr  | ess D/             | ATA (D <sub>7</sub> -D <sub>6</sub> ) | <b>→</b> |

| ALE       |                |                    |                                       |          |

| 10/M,S,So | X              | $IO/M = 1$ , $S_1$ | -1. S <sub>0</sub> -0                 | -/       |

| RD        |                |                    |                                       | _/       |

The steps in I/O Read machine cycle are given in table.

| S. No | T state | Operation              |

|-------|---------|------------------------|

| 1     | T1      | The microprocessor     |

|       |         | places the address of  |

|       |         | the I/O port specified |

|       |         | in the instruction on  |

|   |    | A 1 5 A 0 11 1                                                                                                                                                                                                                                                      |

|---|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |    | A15 – A8 address bus                                                                                                                                                                                                                                                |

|   |    | and also on AD7 -                                                                                                                                                                                                                                                   |

|   |    | AD0 address / data                                                                                                                                                                                                                                                  |

|   |    | bus.                                                                                                                                                                                                                                                                |

| 2 |    | The microprocessor                                                                                                                                                                                                                                                  |

|   |    | makes the ALE signal                                                                                                                                                                                                                                                |

|   |    | HIGH and at the                                                                                                                                                                                                                                                     |

|   |    | middle of T1 state,                                                                                                                                                                                                                                                 |

|   |    | ALE signal goes                                                                                                                                                                                                                                                     |

|   |    | LOW.                                                                                                                                                                                                                                                                |

| 3 |    | The status signals are                                                                                                                                                                                                                                              |

|   |    | changed as $IO/M' = 0$ ,                                                                                                                                                                                                                                            |

|   |    | S1 =1 and S0 = 0.                                                                                                                                                                                                                                                   |

|   |    |                                                                                                                                                                                                                                                                     |

|   |    | These status signals                                                                                                                                                                                                                                                |

|   |    | do not change                                                                                                                                                                                                                                                       |

|   |    | throughout the I/O                                                                                                                                                                                                                                                  |

|   |    | read machine cycle.                                                                                                                                                                                                                                                 |

|   |    |                                                                                                                                                                                                                                                                     |

| 4 | T2 | The microprocessor                                                                                                                                                                                                                                                  |

| 4 | T2 | The microprocessor makes the <i>RD</i> ' line                                                                                                                                                                                                                       |

| 4 | T2 | 1                                                                                                                                                                                                                                                                   |

| 4 | T2 | makes the RD' line                                                                                                                                                                                                                                                  |

| 5 | T2 | makes the RD' line LOW to enable I/O                                                                                                                                                                                                                                |

|   | T2 | makes the RD' line LOW to enable I/O read.                                                                                                                                                                                                                          |

|   | Т2 | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are                                                                                                                                                                             |

|   | T2 | makes the <i>RD</i> ' line LOW to enable I/O read.  The contents on D7 – D0                                                                                                                                                                                         |

| 5 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.                                                                                                                                           |

|   | T2 | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the                                                                                                                   |

| 5 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the address / data bus is                                                                                             |

| 5 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the address / data bus is moved to the                                                                                |

| 5 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the address / data bus is moved to the microprocessor ie., to                                                         |

| 6 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the address / data bus is moved to the microprocessor ie., to the accumulator.                                        |

| 5 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the address / data bus is moved to the microprocessor ie., to the accumulator.  The microprocessor                    |

| 6 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the address / data bus is moved to the microprocessor ie., to the accumulator.  The microprocessor makes the RD' line |

| 6 |    | makes the RD' line LOW to enable I/O read.  The contents on D7 – D0 (i.e. the data) are placed on the address / data bus.  The data loaded on the address / data bus is moved to the microprocessor ie., to the accumulator.  The microprocessor                    |

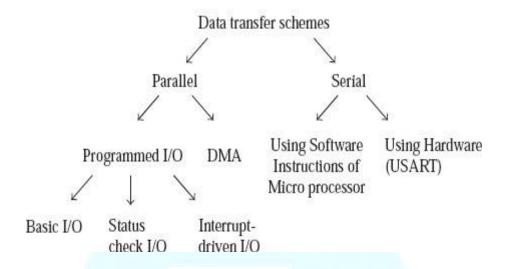

# **DATA TRANSFER SCHEMES OF 8085**

- At the time of executing one 8085 program, interruption can be done in the mid-way by the virtue of the program by an Input Output device.

- Interruption can be done by the method according to which the processor works, since it wants urgent communication with the processor.

- The data transfer schemes always want for sending information to the processor, rather receiving information from the 8085 processor.

- It is so because sending and receiving information in the entire 8085 data transfer scheme process plays a vital role for executing the entire program rather process.

- The communication is not done directly with the Input Output device.

- The communication processes are carried out systematically by the help of Input Output device by the virtue of an Input Output port.

- The data transfer can be either in two forms namely parallel or serial respectively.

- By the virtue of the Programmed Input Access or rather transferring data in parallel the data transfer can be possible by using the Input Output programmed part or by Direct Memory Access (DMA) scheme.

- For transferring data in parallel we have three different ways by means of which microprocessor communicates with an Input or Output. They are:

#### Serial I/O mode transfer

- For these devices and for these above mention reasons serial I/O mode is used.

- In serial I/O mode transfer a single bit of data on a single line at a time.

- For serial I/O data transmission mode, 8-bit parallel word is converted to a stream of eight serial bit using parallel-to-serial converter.

- Similarly, in serial reception of data, the microprocessor receives a stream of 8-bit one by one.

- After receiving serial data, it converted to 8- bit parallel word using serial-to-parallel converter.

- For this purpose data transfer schemes of 8085 microprocessor are introduced.

#### Parallel data transfer scheme

- By the virtue of the Programmed Input Access or rather transferring data in parallel the data transfer can be possible by using the Input Output programmed part or by Direct Memory Access (DMA) scheme.

- Parallel data transfer scheme is faster than serial I/O transfer.

- In parallel data transfer mode, 8-bit data send all together with 8 parallel wires.

- In 8085 microprocessor mainly three types of parallel data transfer scheme we observed. Those are

- Programmed I/O Data Transfer

- Interrupt Driven I/O Data Transfer

- Direct Memory Access (DMA) Data Transfer

- **Basic or simple data transfer scheme**: The simplest data transfer scheme is the basic or simple data transfer. This method is beneficial to us when we have accurate knowledge of the Input Output device timing characteristics.

- Status check data transfer: Status check data transfer process is a much more complex process than simple data transfer. We use this method is used when there is lack of accurate knowledge of the Input Output device consisting of the timing characteristics. Status information is received by the processor regarding the readiness of the Input Output device for performing the data transfer.

- Interrupt driven data transfer: We use this method when there lacks accurate knowledge of the timing characteristics of the Input Output device which takes maximum time for the device to be ready for use. Suppose we resort for the checking of data transfer; the processor here wastes a huge time in the loop for the device to get ready up to the mark.

# APPLICATIONS OF MICROPROCESSOR

- A microprocessor makes daily life easier because of its low cost, low power, small weight, and vast application in every field.

- There are several applications of microprocessors. Some of the important applications are:

### **Household Devices**

- The programmable thermostat allows the control of temperature at homes. In this system, a microprocessor works with the temperature sensor to determine and adjust the temperature accordingly.

- High-end coffee makers, Washing machines, and radio clocks contain microprocessor technology.

- Some other home items that contain microprocessors are: microwaves, toasters, televisions, VCRs, DVD players, ovens, stoves, clothes washers, stereo systems, home computers, alarm clocks, hand-held game devices, thermostats, video game systems, bread machines, dishwashers, home lighting systems and even some refrigerators with digital temperature control.

# **Industrial Applications of Microprocessors**

• Some industrial items which use microprocessors technology include: cars, boats, planes, trucks, heavy machinery, elevators, gasoline pumps, credit-card processing units, traffic control devices, computer servers, most high tech medical devices, surveillance systems, security systems, and even some doors with automatic entry.

### **Transportation Industry**

- Automobiles, trains and planes also use microprocessor technology.

- Consumer vehicles-buses, cars, trucks -integrate microprocessors to communicate important information throughout the vehicle.

- E.g., navigation systems provide information using microprocessors and global positioning system (GPS) technology.

# **Computers and Electronics**

• Microprocessor-drives technology is the brain of the computer.

- They are used in all type of computers ranging from microcomputers to supercomputers.

- A cell phone or mobile device executes game instructions by way of the microprocessor.

- VCRs, televisions and gaming platforms also contain microprocessors for executing complex instructions and tasks.

#### In Medicals

- Many medical devices, like an insulin pump, are typically controlled by a microprocessor.

- The microprocessors perform various functions, such as processing data from biosensors, storing measurements, and analyzing results.

#### Instrumentation

- Microprocessor is also very useful in the field of instrumentation.

- Function generators, frequency counters, frequency synthesizers, spectrum analyses and many other instruments are available, when microprocessors are used as controller.

#### **Entertainment**

• The use of microprocessor in entertainment equipment, toys and home entertaining applications is making them more useful and full of features.

# **Embedded Systems at Home**

- A number of modern devices in the home are microprocessor based i.e. camera; washing machines; calculators; hi-fi systems; telephones; microwave ovens; burglar alarms etc.

- The input are usually simple numeric keyboards, sensors, buttons or while the output include lights, simple LCD screens displays, motors and relays, LEDs, buzzers etc.

### Office Automation and Publication

- Microprocessor based system with software packages has changed the office environment.

- Microprocessors based systems are being used for spread sheet operations, word processing, storage etc.

- The Publication technology has revolutionized by the microprocessor.

#### Communication

- In communication the telephone industry is most important. In this industry, microprocessors are used in digital telephone sets, telephone exchanges and modem etc

- The use of microprocessor in satellite communication, television, has made teleconferencing possible.

- Railway reservation and airline reservation system also uses microprocessor technology. WAN (Wide Area Network) and LAN (Local Area Network) for communication of vertical information through computer network.

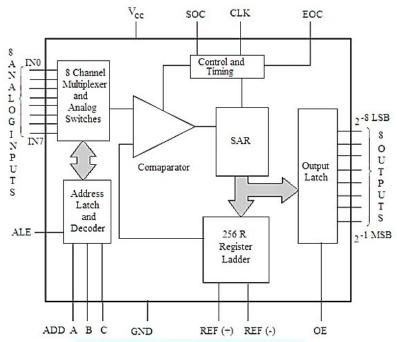

# ANALOG TO DIGITAL CONVERTER

- The Analog to Digital Conversion is a quantizing process.

- Here the analog signal is represented by equivalent binary states.

- The A/D converters can be classified into two groups based on their conversion techniques.

- In the first technique it compares given analog signal with the initially generated equivalent signal.

- In this technique, it includes successive approximation, counter and flash type converters.

- In another technique it determines the changing of analog signals into time or frequency.

- This process includes integrator-converters and voltage-to-frequency converters.

- The first process is faster but less accurate; the second one is more accurate.

- As the first process uses flash type, so it is expensive and difficult to design for high accuracy.

# The ADC 0808/0809 Chip

- The ADC 0808/0809 is an 8-bit analog to digital converter. It has 8 channels multiplexer to interface with the microprocessor.

- This chip is popular and widely used ADC.

- ADC 0808/0809 is a monolithic CMOS device.

- This device uses successive approximation technique to convert analog signal to digital form.

- One of the main advantages of this chip is that it does not require any external zero and full scale adjustment, only +5V DC supply is sufficient.

### **Features of ADC 0808/0809**

- -The conversion speed is much higher

- -The accuracy is also high

- -It has minimal temperature dependence

- -Excellent long term accuracy and repeatability

- -Less power consumption

- -The functional block diagram of this chip is like this

# **Interfacing ADC with 8085 Microprocessor**

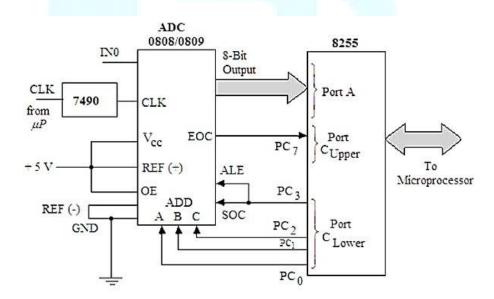

To interface the ADC with 8085, we need 8255 Programmable Peripheral Interface chip with it. Let us see the circuit diagram of connecting 8085, 8255 and the ADC converter.

- The PortA of 8255 chip is used as the input port.

- The PC7 pin of Port C<sub>upper</sub> is connected to the End of Conversion (EOC) Pin of the analog to digital converter.

- This port is also used as input port.

- The C<sub>lower</sub> port is used as output port.

- The PC2-0 lines are connected to three address pins of this chip to select input channels.

The PC3 pin is connected to the Start of Conversion (SOC) pin and ALE pin of ADC 0808/0809.