# **ANALOG ELECTRONICS**

#### JUNCTION THEORY

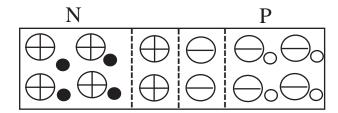

- \* PN Junction is formed on a single crystal of Semiconductor like Ge or Si by dropping acceptor impurity on one side and donor impurity on the other side.

- \* Since P-side is having large hole as compared to electron and N-side is having large electron as compared to hole so due to difference in concentration, diffusion takes place, i.e., hole diffuse to N-side and electron diffuse to P-side.

- \* Depletion region is completely free from any mobile charge. It is behave just like Capacitor, which is controlled by appled voltage at P and N side.

- \* Forward bias causes Depletion region to shrink, so increase the value of capacitor.

- \* Total Depletion region width  $W = W_n + W_p$

- \*  $N_DW_n = N_AW_P$  means for highly dropped region the Depletion region is less in that side.

- \* Barrier Potential or Build in Potential.

$$V_B \ = \ V_T \ \ell n \left( \frac{N_A. \ N_D}{n^2} \right) \quad \ = \ \frac{KT}{q} \ \ell n \left( \frac{N_A. \ N_D}{n^2} \right)$$

\* Current flow in PN junction diode =  $I_0 \left( \frac{nv}{v_T} - 1 \right)$

Where  $I_0$  = reverse saturation current

n = Factor due to charge generation and recombination.

n = 1 for Ge. = 2 for Si

\* I<sub>0</sub> doubles for every 10°C rise in temp.

$$I_0' = I_0 2^{[(T'-T)/10]}$$

\* Diode dynamic resistant

$$r = \frac{dV}{dI} = \frac{1}{dI/dV} = 1/Slop \text{ of characteristic of diode}$$

$$= \frac{nV_T}{I} = \frac{26(mV)}{I(mA)} \quad ; \quad n = 1$$

$$* \quad I_o = q \left( n_p \frac{L_n}{\tau_n} + p_N \frac{L_p}{\tau_p} \right)$$

Where,  $L_n$  and  $L_p \rightarrow Diffusion length$  $\tau_n$  and  $\tau_p \rightarrow \text{Life time.}$

#### CAPACITANCE IN PN JUNCTION DIODE

The depletion region denotes a parallel plate capacitor since the total charge on the 2 side of the depletion region is equal but opposite.

$$C = \frac{\varepsilon A}{d} = \frac{\varepsilon A}{w}$$

$$Where, \ \varepsilon = \text{permittivity of medium}$$

$$A = \text{cross section area}$$

$$d = W = \text{Total width of depletion region.}$$

$$= W_N + W_P$$

Capacitance are of two type

# TRANSITION CAPACITANCE

C<sub>T</sub> arises due to reverse bias applied and due to majority charge carrier.

$$C_{T}(V_{r}) = \frac{C(o)}{1 + \left[V_{r}/V_{T}\right]} n$$

$V_r$  = Reverse bias voltage;

C(o) = Capacitance at zero bias;

n = [1/2] for step graded/Abrupt junction

= [1/3] for diffused/linearly graded junction.

Finally,  $C_T = K_1[V]^{-1/2}$ : for abrupt junction  $= K_2 V^{-1/3} : \text{ for linearly graded function}$   $W_B = K_1[V_j]^{1/2} : \text{ for abrupt junction}$   $= K_2[V_j]^{1/3} : \text{ for linearly graded junction.}$

Diffusion Capacitance C<sub>D</sub> exist for forward bias and is important for minority charge carrier

$C_D = \frac{\tau_n}{r_n} + \frac{\tau_n}{r_p}$

Where,  $\tau = \text{Life time};$

r = Dynamic resistance of region

- \* Diffusion Capacitance increase rapidly with forward bias i.e.  $C_D \propto I$ .

- \* The value of C<sub>D</sub> is of the order of several  $\, \triangleright F$  and hence it is important when high frequency circuit for transistor are derived.

- \* Voltage variable diode capacitor are called Varactor, Varicap or Volta cap. They are used in frequency modulation circuit.

\*  $L = \sqrt{D \tau}$

Where L = Diffusion length, D = Diffusion Coefficient

$\tau$  = Life time

The Einstein relation

$$\frac{D}{\mu} = V_T = \frac{KT}{q}$$

# DIFFERENT TYPES OF DIODES AND THEIR CHARACTERISTIC

### **DIODE**

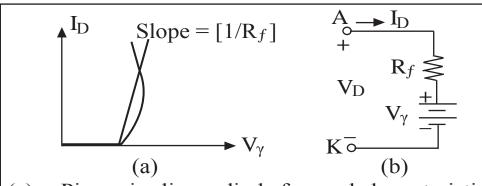

- (a) Piecewise linear diode forward characteristic

- (b) Diode model for forward bias.

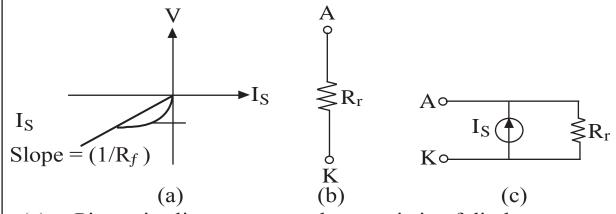

- (a) Piecewise linear reverse characteristic of diode

- (b) Diode model based on piecewise linear representation.

- (c) Model to include surface leakage

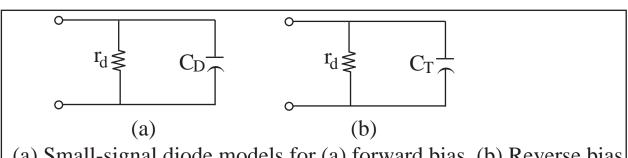

(a) Small-signal diode models for (a) forward bias (b) Reverse bias

$-V_R$

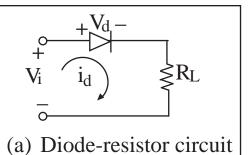

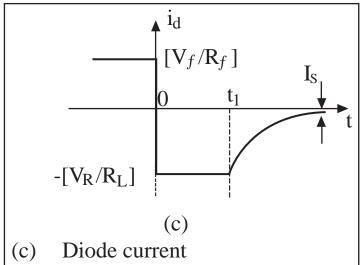

(b) Input waveform applied to circuit in part figure (a) Showing abrupt change from forward to reverse bias.

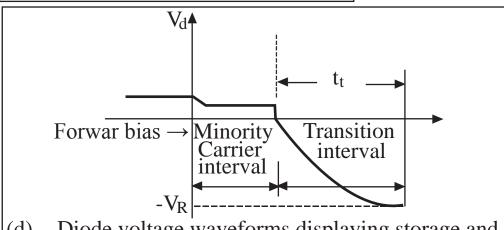

Diode voltage waveforms displaying storage and (d) transition times.

#### ZENER DIODE

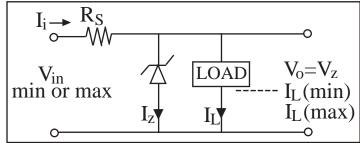

It is a PN junction diode with heavy doping Operate under reverse bias condition and for voltage  $> V_{\rm g}$  . (Breakdown voltage)

#### **BREAKDOWN MECHANISM**

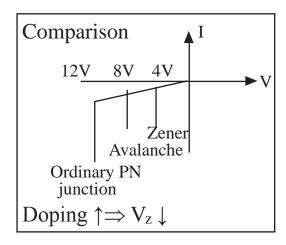

Zener breakdown and Avalanche breakdown

#### Zener Breakdown

- 1. This phenomenon occur in PN junction diode with very high doping.

- 2. It occur when the diode is reverse bias of voltage approximately 4 to 6 V.

- 3. The junction is narrow since the width of depletion layer is small become of highest doping and relatively low reverse bias voltage.

- 4. The junction width is of the order of  $100A^{\circ}$  so that very strong electric field of  $10^{7}$  V/m is developed near the junction

- 5. Now as the reverse bias voltage is increased then the current will be only due to minority charge and is of the order is  $\mu A$  or nA.

- 6. As the reverse voltage is still increased a value of this voltage is reached so that very high electrical field is developed.

- 7. For this magnitude of the electrical field there will be direct rupture of the covalent bond so that immediately a number of free charge carrier is generated.

- 8. At this voltage we say that the zener breakdown has occur and because of increase number of free charge carrier conductivity of the region increases.

- Therefore, the current suddenly increasing maintaining a constant potential across the PN junction. This constant voltage is called the zener breakdown voltage.

- $9. \hspace{0.5cm} V < V_z \hspace{0.5cm} ; \hspace{0.5cm} I \, \cong \, 0$

- $V \ge V_z$  ; I = Suddenly increase

- 10.  $V < V_z$  The dynamic resistance is very large  $V \ge V_z$  The dynamic resistance is small.

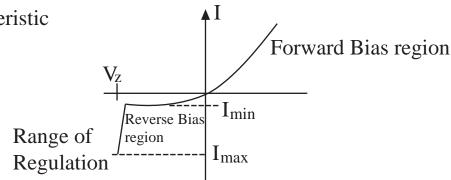

11. Characteristic

- 12. In the forward bias condition the V I characteristic is of the similar nature of ordinary diode.

- 13. The V I characteristic of forward bias condition is not practically useful since the same variation we can get using an ordinary PN junction diode.

- 14. The increase in the current, once the breakdown has occur is limited by the use of a series of resistor along with the zener diode the current varies from  $I_{min}$  to  $I_{max}$ .  $I_{max} = I$  (rated current)

- 15. Practically for designing a circuit, we use  $I_{min}$  to the 20% of 1 (rated).  $I_{min} \cong 0.2 \text{ I rated}$   $I_{max} = 0.8 \text{ I(rated)}$

- 16. This device can be utilized as a voltage regulator since the voltage across it remain constant irrespective of current variation through it.

## **Avalanche Breakdown**

- 1. This breakdown occurs in PN junction diode with reverse bias applied.

- 2. The doping in much greater than that used in the ordinary PN junction diode but is smaller than that of a diode in which zener breakdown occur, i.e.  $D_{zener} > D_{-avalanche} > D_{-ordinary}$

- 3. The reverse bias voltage applied relatively higher of the order of 8 to 10 V depending upon doping.

- 4. The width of depletion layer is relatively more than that in the diode with zener breakdown.

- 5. Since the reverse bias voltage applied is relatively large an free charge carrier say electron acquire high K.E and strike an atom. The covalent bond is broken and other free-electron is librated so that now there are two free electron available for conduction.

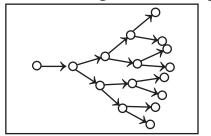

- 6. Since the applied voltage is maintained high there two electrons again acquire high K.E., striking other atom and librating two more free electron ad so on.

- 7. At a given voltage called the avalanche breakdown voltage a number of free charge carrier are available to avalanche multiplication as shown so that the conductivity of the region suddenly increase.

Therefore the current suddenly increase maintaining a constant pote-

ntial to the junction.

# Variation Vz with temperature

Dynamic Resistance  $r = \frac{\Delta V}{\Lambda I}$

- = Very large for  $V < V_z$

- = Very small for  $V > V_z$

- 8. The VI characteristic is similar to that a diode with zener breakdown.

# CHARACTERISTICS OF BJT BJT: BIPOLAR JUNCTION TRANSISTOR

Collector region width is maximum

(a) To collect maximum number of charge carrier.

| N     | E <sub>j</sub> P C <sub>j</sub> N |                           |  |

|-------|-----------------------------------|---------------------------|--|

| Е     | В                                 | С                         |  |

| $J_1$ |                                   | $\overline{\mathrm{J}_2}$ |  |

(b) To reduce heat dissipation (per unit area surface).

Depletion layer in collector junction base side is maximum Emitter junction. Emitter side is Minimum.

Biasing and application

| Input Jn J <sub>1</sub> | Output Jn J <sub>2</sub> | Region in which   | Application                        |

|-------------------------|--------------------------|-------------------|------------------------------------|

| (EB J <sub>n</sub> )    | $(CB J_n)$               | BJT works         |                                    |

| FB                      | RB                       | Active            | Amplifier                          |

| FB                      | FB                       | Saturation        | BJT is ON or OFF                   |

| RB                      | RB                       | Cut off           | OFF                                |

| RB                      | FB                       | Invented (Active) | Amplifier with dec-                |

|                         |                          |                   | reased gain $\alpha_1$ , $\beta_1$ |

<sup>\*</sup> For Normal Biasing (i.e. Emitter junction FB and Collector junction RB) the emitter junction has low resistance.

#### **EARLY EFFECT**

For active region operation of transistor collector base region is reversed biased. Due to reverse bias the depletion width in base region increases which causes effective width of base to decrease. This effect is known as early effect.

If the reverse bias VcB is increased beyond a point, breakdown may occur as width of base becomes zero and phenomena is called punch through or Base width modulation.

#### THE PHYSICAL BEHAVIOR OF BIPOLAR TRANSISTOR

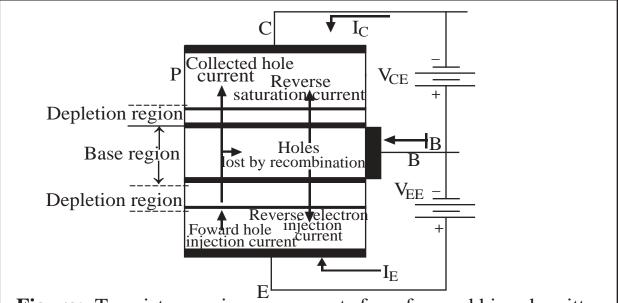

**Figure:** Transistor carrier components for a forward biased emitter-base junction and reverse biased collector base junction.

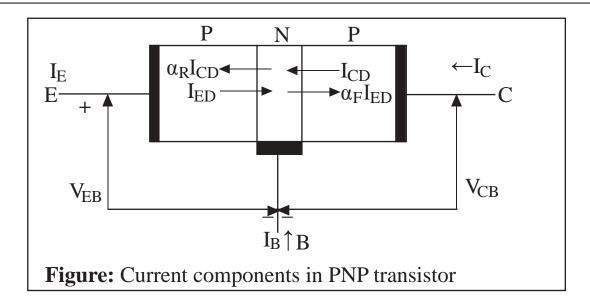

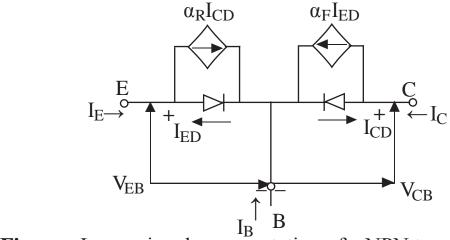

On the basis of the considerations in the preceding paragraph we construct the Ebers-Moll mode in below figure. The two back to back diode (whose cathodes are connected) represent the junctions of the bipolar transistor, whereas the two controlled sources indicate the coupling

between junctions.

The current  $I_{ED}$  and  $I_{CD}$  are related to  $V_{EB}$  and  $V_{CB}$  by the diode volt ampere relation given in the equation. Thus the  $I_E$  and  $I_C$  can be expressed in terms of the two diodes currens as

**Figure:** Large-signal (Ebers-Moll) representation of a PNP transistor.

$$\begin{split} I_{E} &= I_{ED} - \alpha_{R} I_{CD} = I_{ES} \left[ \left( e^{V_{EB}/V_{T}} \right) - 1 \right] - \alpha_{R} I_{CS} \left( e^{V_{CB}/V_{T}} \right) \\ I_{C} &= -\alpha_{R} I_{ED} + I_{CD} = -\alpha_{F} I_{ES} \left( e^{V_{EB}/V_{T}} - 1 \right) + I_{CS} \left( e^{V_{CB}/V_{T}} - 1 \right) \end{split}$$

The relationship expressed in above two equations are known as the Ebers-Moll equations.

The quantities  $I_{ES}$  and  $I_{CS}$  in above equation are reverse saturation currents of emitter ase and collector base junction, respectively. The parameter  $\alpha_F$  and  $\alpha_R$  are each less than unity as not all the current from

one diode is couple to the other junction. The subscript refer to forward (F) transmission from emittor to collector and reverse (R) transmission from collector to emitter.

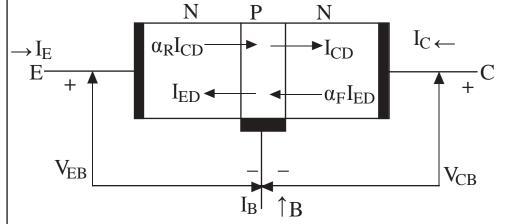

$$\begin{split} &\alpha_F \, I_{ES} \, = \alpha_R I_{CS} \quad \text{and} \quad I_B \ \, = - \left( I_E \, + I_C \, \right) \\ &I_E \ \, = -I_{ES} \left[ e^{\left( \frac{V_{EB}}{V_T} \right)} - 1 \, \right] + \alpha_R \, I_{CS} \left[ e^{\left( \frac{V_{CB}}{V_T} \right)} - 1 \right] \\ &I_C \ \, = \alpha_F \, I_{ES} \left[ e^{\left( \frac{V_{EB}}{V_T} \right)} - 1 \, \right] - I_{CS} \left[ e^{\left( \frac{V_{CB}}{V_T} \right)} - 1 \right] \end{split}$$

Figure: Current component in NPN transistor

**Figure:** Large-signal representation of a NPN transistor

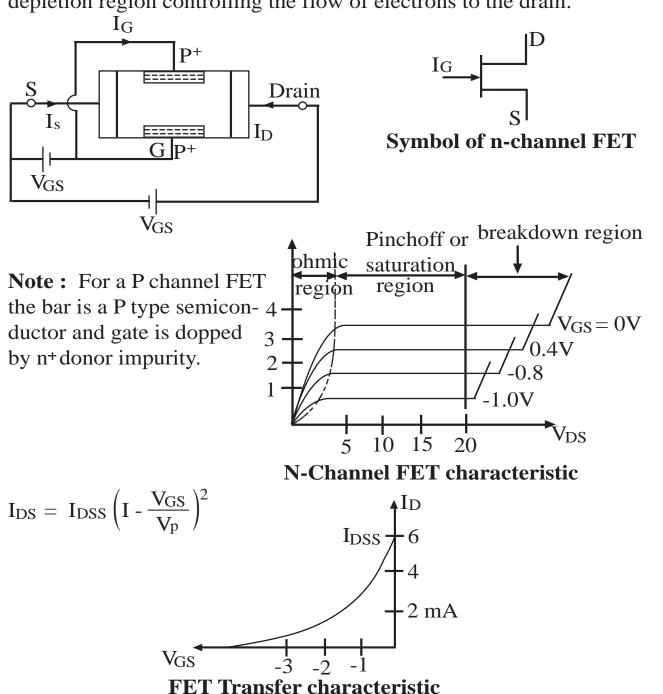

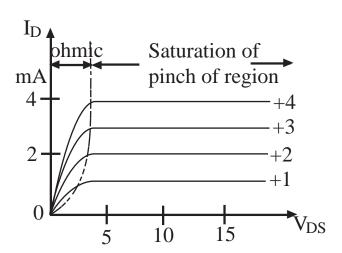

# CHARACTERISTICS OF JFET TWO TYPES: N CHANNEL AND P CHANNEL

It consists of a semiconductor block which is n type for n channel and p type for p channel. On both sides of n block acceptor impurities p are heavily doped by allowing or by diffusion. The region is called the gate. Ohmic contact are attached to the either ends of the n-block. One end is called Source and other is called Drain. The np region between source

and gate is reverse biased. In the vicinity of np junction there is diffusion of majority carriers, electrons and holes leaving uncover immobile positive and negative ions. When RB is applied, the space charge width increases uncovering more ions, until the space charge region from the two end, meets the n type region between the two (P+) gates is called n channel and when a positive voltage is applied between drain and source, there is a current flow in the channel of majority carriers, (electrons). When a reverse bias is applied between the gate and source, constriction of the channel takes place by widening of the space charge depletion region controlling the flow of electrons to the drain.

**Page - 11**

1. Drain resistance

$$r_d = \frac{V_{DS}}{I_D} \Big|_{V_{GS} = Constant}$$

Output resistance of FET and evaluated in constant drain current region of  $V_{DS}$  -  $I_D$  curve. It is of the order of 10 to 20 k $\Omega$ s.

2. Transconductance

$$g_m = \frac{I_D}{V_{GS}} \Big|_{V_{DS} = Constant}$$

It will be of the order of 2 k to 6 k micromhos.

3. Amplification Factor

$$\mu = g_m r_d$$

4.

$$=\frac{V_{DS}}{I_D} \times \frac{I_D}{V_{GS}} = \frac{V_{DS}}{V_{GS}}$$

, It ranges of 40 to 100.

5. Input resistance

$$r_{GS} = \frac{V_{GS}}{I_{GSS}}$$

It is of the order of hundruds of megaohmes. FET is high impedance device.

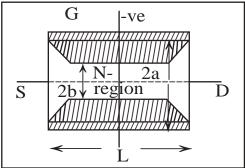

#### **VARIOUS RELATIONSHIP OF FET**

Pinch off voltage

$$V_p = \frac{eN_D a^2}{2\epsilon}$$

$2a \rightarrow \text{Width of channel without any gates bias.}$

$2b \rightarrow Width of channel after bias.$

$L \rightarrow Length of the channel.$

$$b = a \left[ 1 - \left( \frac{V_{GS}}{V_p} \right)^{1/2} \right]$$

; when  $V_{GS} = 0$ ,  $b = a$

If  $w \rightarrow$  channel dimension perpendicular to b direction.

$$A = 2bW$$

Drain Current  $I_D = AqN_D \mu_n E = 2bwq N_D \mu_n \frac{V_{DS}}{L}$

Substituting 'b'

$$I_D = \frac{2awqN_D\mu_n}{L} \left[1 - \left(\frac{V_{GS}}{V_p}\right)^{\!\!1/2}\,\right] \ V_{DS}$$

The ON resistance

$$\ r_d = \frac{V_{ds}}{I_d}$$

$$\ r_{dON} = \frac{L}{2awqN_D\,\mu_n} \ \ \text{for} \ \ V_{GS} = 0$$

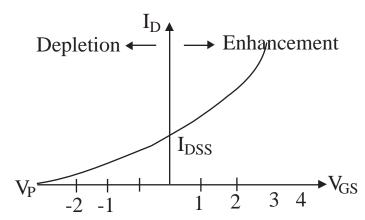

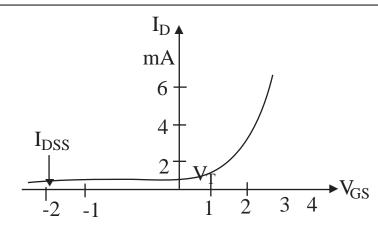

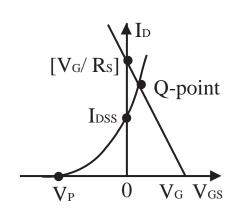

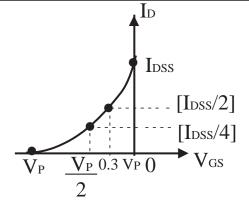

**Transfer Characteristics**

In amplifier application, the FET is almost used in the region beyond pinch-off (also called the constant-saturation region).

$$I_{DS} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_p} \right)^2$$

Relation between  $g_m$ ,  $I_{DDS}$  and  $I_{DS}$

$$I_{DS} = I_{DSS} \left(1 - \frac{V_{GS}}{V_p}\right)^2 \dots (1)$$

$$\frac{\partial I_{DS}}{\partial V_{GS}} = I_{DSS} 2 \left(1 - \frac{V_{GS}}{V_p}\right) \left(\frac{-1}{V_p}\right)$$

$$g_{\rm m} = \left(\frac{-2I_{\rm DDS}}{V_{\rm p}}\right) \left(1 - \frac{V_{\rm GS}}{V_{\rm p}}\right) \dots (2)$$

$$g_{mo} = \text{It is value of } g_m \text{ for } V_{GS} = 0 \text{ and given by } g_{mo} = \left(\frac{-2I_{DSS}}{V_p}\right) \dots (3)$$

now

$$g_{m} = g_{mo} \left( 1 - \frac{V_{GS}}{V_{p}} \right) ...(4)$$

$$I_{DS} = \frac{1}{V_{GS}} \left( \frac{V_{GS}}{V_{p}} \right) ...(4)$$

From equation (1)

$$\left(1 - \frac{V_{GS}}{V_p}\right) = \sqrt{\frac{I_{DS}}{I_{DSS}}} \qquad ...(5)$$

From equations (2) and (5)

From the transfer characteristic we have

$$g_m = \frac{-2I_{DSS}}{V_p} \sqrt{\frac{I_{DS}}{I_{DSS}}} = \frac{-2}{V_p} \sqrt{I_{DS} \cdot I_{DSS}}$$

$$|g_m| = \frac{2}{|V_p|} \sqrt{I_{DS} \cdot I_{DSS}}$$

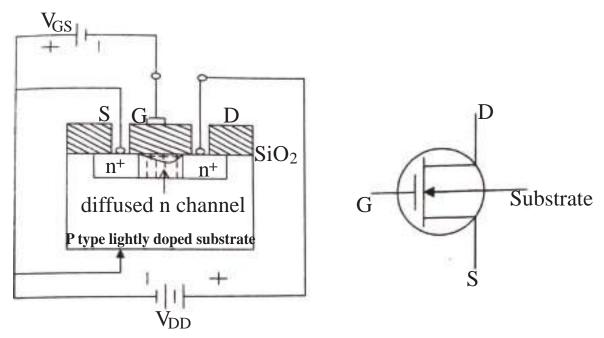

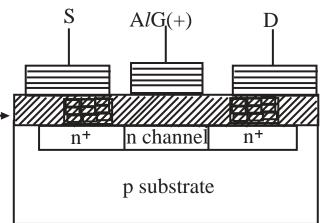

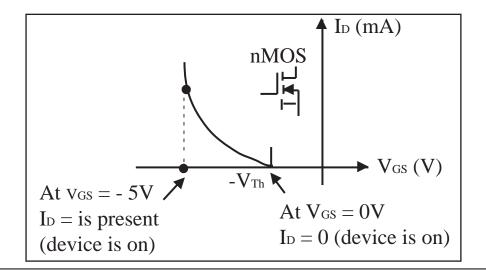

# CHARACTERISTICS OF MOSFET DEPLETION TYPE MOSFET

The real name of MOSFET is IG FET, i.e., insulated gate field effect transistor. The gate insulated from the substrate by an oxide layer.

In the FET the metal and channel with dielectric in between forms a parallel plate capacitor giving rise to a high input impedance of  $(10^{10})$  to  $(10^{15})$  ohms and is the major difference from JFET. There are two types of MOS-FET enhancement and depletion type.

**Figure:** Symbol of n channel depletion type MOSFET

When a negative voltage  $V_{GS}$  is applied to the conducting terminal of the capacitor positive charges are induced in the channel, the other side of the capacitor. These positive charge neutralize the electrons in the n channel and reduce the charge carrier. This reduces the drain current. The depletion region is wider as in JFET near the drain than the near the source, due to voltage drop by the drain current. Unlike JFET when gates is reverse biased, MOSFET there is no pn $^+$  junction. As the carrier, electron, in n channel are depleted this is called depletion type MOSFET. The same MOSFET can be made enhancement type when a positive vol-

tage is applied to the gate negative charge are induced in the channel adding to the electron, charge carrier in the channel this enhances the drain

**Depletion MOSFET Characteristic**

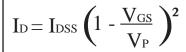

**Depletion N-MOSFET Transfer Characteristic**

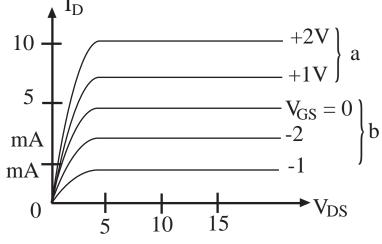

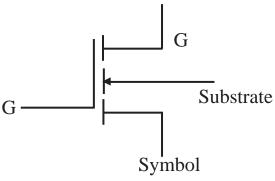

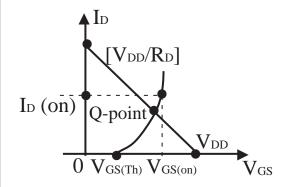

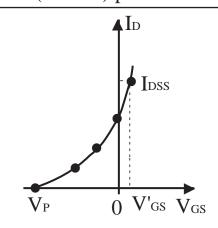

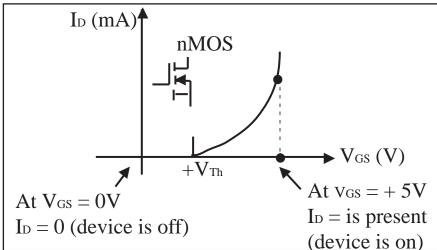

#### ENHANCEMENT TYPE MOSFET

No channel is diffused in the P substrate. So when a positive voltage is

applied to the gate, the minority carries is the P substrate, electrons are drawn towards the dielectric and this forms an effective channel. As the positive voltage on the Sio₂ → gate is increased, conductivity increases leading to higher drain current as the negative charge carrier are increased.

(Positive Gate voltage greater than  $V_T$  is applied) **Figure :** Enhancement in n-channel MOSFET

**Figure :** Symbol of n-channel enhancement MOSFET

**Enhancement N-MOSFET Characteristics**

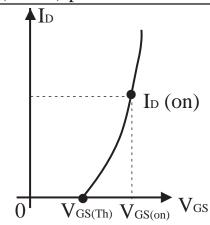

Figure: Transfer characteristic of N-channel E-MOSFET

- \* We note from the transfer characteristics that a threshold voltage V<sub>GST</sub> is required for drain current to flow. Without gate voltage, a small current of nanoampere I<sub>D</sub> flows in the drain.

- \* The electric field produced by the gate voltage is largest near the source and least near the drain.

- \* For pinch of  $V_{PDS} = V_{GS} V_T$

## **Compassion between FET ad SMOSFET**

- 1. A current-controlled device is one in which a current defines the operating conditions of the device, whereas a voltage-controlled device is one in which a particular voltage defines the operating conditions.

- 2. The JFET can actually be used as a voltage controlled resistor because of a unique sensitivity of a the drain-to-source impedance to the gate-to-source voltage.

- 3. The maximum current for any JFET is labeled  $I_{DSS}$  and occurs when  $V_{GS} = 0 \text{ V}$ .

- 4. The minimum current for a JFET occurs at pinch-off defined by  $V_{GS} = V_P$ .

- 5. The relationship between the drain current and the gate to source voltage of a JFET is a nonlinear one defined by Shockley's equation. As the current level approaches I<sub>DSS</sub> the sensitive of I<sub>D</sub> to changes in V<sub>GS</sub> increases significantly.

- 6. The transfer characteristics ( $I_D$  versus  $V_{GS}$ ) are characteristics of the device itself and are not sensitive to the network in which the JFET is employed.

- 7. When  $V_{GS} = V_P/2$ ,  $I_D = I_{DSS}/4$ ; and a point where  $I_D = I_{DSS}/2$ ,  $V_{GS} = 0.3 \ V$ .

- 8. Maximum operating conditions are determined by the product of the drain-to-source voltage and the drain current.

- 9. MOSFETs are available in one of two types: depletion and enhancement.

- 10. The depletion-type MOSFETs has the same transfer characteristics as a JFET for drain currents up to the I<sub>DSS</sub> level. At this point the characteristics of a depletion point type MOSOFET continue to levels above I<sub>DSS</sub>. Whereas those of the JFET will end.

- 11. The arrow in the symbol of n-channel JFETs or MOSFETs will always point in to the center of the symbol, whereas those of a p-channel device will always point out of the center of the symbol.

- 12. The transfer characteristics of an enhancement-type MOSFET are not defined by Shockly's equation but rather by a nonlinear equation controlled by the gate to source voltage, the threshold voltage, and a constant k defined by the device employed. The resulting plot of I<sub>D</sub> versus V<sub>GS</sub> is one that rises exponentially with increasing values of V<sub>GS</sub>.

- 13. Always handle MOSFETs with additional care due to the static electricity that exists in places we might least suspect. Do not remove any shorting mechanism between. The device until it is installed.

- 14. A CMOS (complementary MOSFET) device is one that employs a unique combination of a p-channel an n-channel MOSFT with a single set of external leads. It has the advantages of a very high input impedance, fast switching speeds, and low operating power levels, all of which make very useful in logic circuits.

$$\begin{split} \textbf{JFET} \\ I_D &= I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2 & I_D &= I_{DSS} \,_{V_{GS} \,=\, 0V} \; ; \; I_D \,=\, 0 \,\, \text{mA} \Big|_{V_{GS} \,=\, V_P} \\ I_D &= \frac{I_{DSS}}{4} \Big|_{V_{GS} \,=\, V_P/2} & V_{GS} \,=\, 0.3 \,\, V_P \Big|_{I_0 \,\,=\, I_{DSS/2}} \; ; \; V_{GS} \,=\, V_P \left( 1 - \sqrt{\frac{I_D}{I_{DSS}}} \right) \\ P_D &= V_{DS} \, I_D & r_d \,\,=\, \frac{r_0}{(1 - V_{GS}/V_r)^2} \end{split}$$

$$I_{D} = k(V_{GS} - V_{T})^{2}$$

$k = \frac{I_{D(on)}}{(V_{GS(on)} - V_{T})^{2}}$

## **Typical values for JFET and MOSFET**

| Parameter                             | JFET            | MOSFET            |

|---------------------------------------|-----------------|-------------------|

| Input resistance r <sub>gs</sub>      | $> 10^9 \Omega$ | $> 10^{13}\Omega$ |

| Transconductance                      | 1 K to 2.5 K    | 1 K to 20 K       |

| g <sub>m</sub> (μ mho)                |                 |                   |

| Drain resistance r <sub>d</sub> (ohm) | 0.1 M to 1 M    | 1 K to 50 K       |

| Revere current I <sub>GSS</sub>       | 0.1 to 10 nA    | 0.1 to 10 pA      |

| Capacitance C(G to D)                 | 1 to 4 pF       | 0.005 to 1 pF     |

#### For D-MOSFET

Characteristic are similar to FET

For E-MOSFET

$$V_{DS sat} = V_{GS} - V_{T}$$

For  $V_{GS} << V_{T}$ , the drain current of an enhancement type MOSFET is 0 mA.

For levels of  $V_{GS} > V_T$ , the drain current is related to the applied gate-to-source voltage by the following nonlinear relationship.

$$I_D = K(V_{GS} - V_T)^2$$

Where,  $K \rightarrow$  constant that is function of the construction of the device, the value of K can be determined from

$$\begin{array}{cc}

\text{III} \\

\text{K} &= \frac{I_{\text{D(on)}}}{(V_{\text{GS(on)}} - V_{\text{T}})^2}

\end{array}$$

$I_{D(on)}$  and  $V_{GS(on)}$  are the values for each at a particular point on the characteristic of the device.

## **Compassion between BJT and FET**

|    | BJT                      | FET                  |

|----|--------------------------|----------------------|

| 1. | High voltage gain        | Low voltage gain     |

| 2. | Low current gain         | High current gain    |

| 3. | Low input and            | High input and       |

|    | output impedance         | output impedance     |

| 4. | Medium noise generation  | Low noise generation |

| 5. | (Gain × band-width) high | (Gain × Band-width)  |

|    |                          | medium               |

| 6. | Current source           | Voltage controlled   |

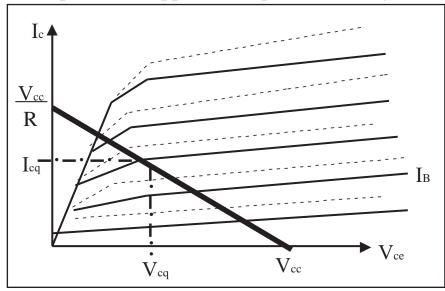

## **Biasing and Stabilization**

The transistor is biased (with the help of external voltage in such a manner so the Q-point is selected in the middle portion the transistor output characteristic. When the ac voltage is superimposed it is ensure that the positive and negative half of input voltage cycle remain it the linear or active region if the transistor characteristic. Under these condition the transistor output voltage is undistored.

- To fix the Q-point load line curve is needed.

- The dc load line is locus of variation of output voltage and output current.

- The load lines are being drawn for the amplifier chosen in the active region of output of characteristic.

- The Q-point is generally fixed at the middle of load line.

- Ac load line have greater slope than dc load line.

- If the Q-point is chosen near the V<sub>ce</sub> (Cut-off region or I<sub>c</sub> axis (saturation region) than output will be highly distorted.

- If the Q-pont is chosen in the saturation region for NPN transistor, it may cause the output to be clipped in the positive half cycle of the input signal.

#### **Stabilization**

Once the Q-point has been fixed due to some biasing arrangement it has to be stabilized against the variation in :

- (a) Temperature (T)  $I_{co}$  double for every 10 degree rise in temperature.

- (b) I<sub>B</sub> (depends on V<sub>be</sub>), i.e. V<sub>be</sub> decrease at the rate of 2.5 mv/degree.

- (c) β

- Due to variation of one or all of these parameter I<sub>c</sub> current will change which shift the Q-point.

- In stabilization technique resistive biasing circuit is used which permit I<sub>b</sub> to

vary by an amount so as to keep  $I_c$  relatively constant with variation in any of T,  $I_b$ , $\beta$

# **Change in Temperature**

- We know that  $I_c = \beta I_b + (1 + \beta) I_{co}$

- $\beta$  varies due to change in temp.

- I<sub>b</sub> also change due to change in temp. As the cut in voltage is increases at 2.5 mv/degree for constant I<sub>c</sub>.

- I<sub>co</sub> changes with temperature doubling with every 10 degree rise in temperature. Increase in I<sub>co</sub> caused an increase in I<sub>c</sub> which further increasing the collector dissipation thereby increasing the collector temperature. This may set in a cumulative effect causing thermal runway burning out the transistor ultimately.

- = Si transistor, I<sub>co</sub> is of the order of nano amperes compared to milliamps in Ge and so thermal runway and instability is more problem in Ge transistor.

# **Stability Factor**

• The merit of a biasing circuit in holding the dc collector current I<sub>c</sub> at the operating Q-point may be examine by stability factor.

$$S = \frac{\delta I_c}{\delta I_{co}} | V_{be}, \beta = constant$$

$$S_{\beta} = \frac{\delta I_{c}}{\delta \beta} \left| I_{co} \right| V_{be} = constant$$

$$Sv = \frac{\delta I_c}{\delta V_{bo}} \left| I_{co} , \beta = constant \right|$$

- Lower the value of stability factor (S) better is stability of circuit.

- $1 < S < 1 + \beta$

- ullet The stability factor S is most important since it depends upon  $I_{co}$  and temperature.

$$S_{\beta} = \frac{\delta I_{c}}{\delta I_{\infty}} \bigg|_{V_{be} = Constant}$$

$I_c = \beta I_b + (1 + \beta) I_{co} \dots$  generally expression

Differential with respect to Ic

$$1 = \beta \frac{\delta I_b}{\delta I_c} + (1 + \beta) \frac{\delta I_{co}}{\delta I_c}$$

$$S = \frac{\delta I_c}{\delta I_{co}} = \frac{(1+\beta)}{(1-\beta)\frac{\delta I_b}{\delta I_c}}$$

• For fixed bias arrangement Ib is independent of Ic,

$$S = \beta + 1$$

• Collector to base biasing:

$$S = \frac{1 + \beta}{1 + \frac{\beta R_c}{R_b + R_c}}$$

- (a) Better than fixed biased circuit.

- (b)  $\beta R_c \gg R_b$  as this will give very small value as stability as near to 1.

#### **Drawback of Collector to Base Bias**

- R<sub>b</sub> has to be very small but this gives large I<sub>b</sub>. This increase in I<sub>b</sub> is offset by a decrease in I<sub>b</sub> hence there is not much overall improvement in stability.

- Output is feedback to the base via R<sub>b</sub> and this reduces the net gain of the transistor.

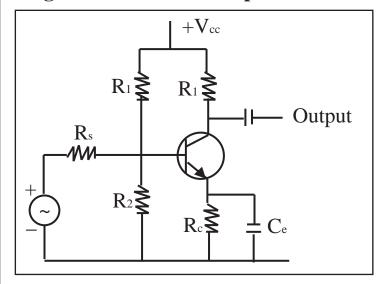

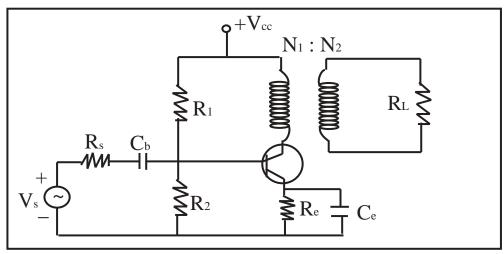

#### Self-Bias/ Potential Divider/ Emitter Bias

- As compared to collector-base bias, if the load of the collector is a transformer, then  $R_c$  will be small so  $\beta R_c >> R_b$  cannot be achieved. But selfbias is suitable for any type of load resistance.

- Emitter bias is applied by a resistor Rs between the emitter and ground i.e, Thevenin equivalent of two resistor of self bias.

- When collector current increased the voltage drop across  $R_c$  increases and reduce forward bias  $V_{be}$  reducing base current  $I_b$  and keeping the operaing point stable.

- Stability factor

$$S = \frac{1 + \beta}{1 + \frac{\beta R_c}{R_b + R_c}}$$

- $R_e \gg R_b$ , S = 1 Best stability

- Re introduces both dc and ac feedback.

- In order to avoid the loss of ac signal gain because of feedback caused by Re This R<sub>e</sub> is by passed by a leakage capacitor C<sub>e</sub> of high value so that is offering little resistance at frequency of interest.

$$\begin{split} S_{\beta} &= \frac{\delta I_c}{\delta \beta} \quad ; \quad S_{\beta} = \frac{I_{C1} \cdot S_2}{\beta_1 (1+\beta)} \\ S_v &= \frac{\delta I_c}{\delta V_{be}} \quad ; \quad S_v = \frac{\beta}{R_b + R_c \left(1+\beta_2\right)} \end{split}$$

where  $S_2$ : Stability (S) at  $\beta = \beta_2$

Total increment in  $I_c$  is the sum of all there increaments due to  $I_{co}$ ,  $\beta$  and  $V_{be}$

$$\Delta I_c = S_1 \; . \Delta I_{co} + S_v \; . \; \Delta V_{be} + S_\beta \; \Delta \beta$$

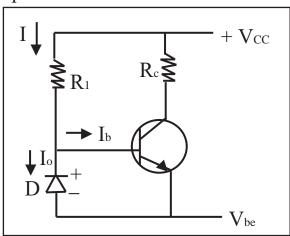

# **Compensation Techniques**

- Major disadvantage of the resistor biasing techniques is the feedback of the output signal to input which causes reduction in gain. To avoid this, compensation technique with diodes, transistor and Thermsitor are employed.

- Diode compensation.

- Reversed biased diode is connected in the base emitter circuit, which is same material as transistor.

- The reverse bias voltage  $V_{be}$  allowing the reverse saturation current to  $I_0$  to flow through the diode D.

$$I = \frac{V_{cc} - V_{be}}{R_l} = \frac{V_{cc}}{R_l}$$

And  $I_B = I - I_o$

From collector current expression

$$I_c = \beta I_b + (1 + \beta) I_{co} = \beta I - \beta I_o + (1 + \beta) I_{co}$$

=  $\beta I$  -  $\beta I_0$  +  $\beta I_{co}$  if  $\beta$  >> 1 and  $I_0$  of diode and  $I_{co}$  of transistor track each other over the desired temperature rang, then  $I_{co}$  remains essentially constant. Reverse saturation current  $I_0$  flows through the diode. If  $I_{co}$  increases due to temperature, the increased current flows through diode decreasing  $I_b$  keeping  $I_b$  constant.

#### **Thermistor**

Thermistors are temperature sensitive element, which has a negative temperature coefficient of resistance.

The thermistor element is placed parallel to and across V<sub>cc</sub> and E. R<sub>2</sub> of potential divider bias. Increase of temperature reduces resistance and decrease the forward bias reduces I<sub>b</sub> and I<sub>c</sub>.

# **Sensistor Compensation**

It may be placed either in parallel with  $R_1$  or parallel with  $R_E$ . It can also be placed in place of  $R_E$  rather than in parallel with  $R_E$ .

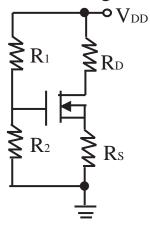

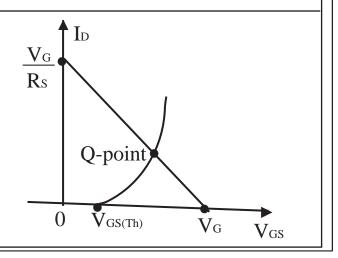

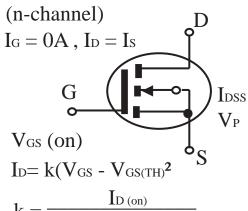

### FET/ MOSFET Biasing

For the field effect transistor, the relationship between input and output quantities is nonlinear due to the squared term in Shockley's equation. The non linear relationship between I<sub>D</sub> and V<sub>GS</sub> can complicated the mathematical approach to the dc analysis of FET configurations. A graphical approach may limit solutions to tenths-place accuracy, but it is a quicker method for most FET amplifiers.

Another distinct difference between the analysis of BJT and FET transistors is that the input controlling variable for a BJT transistor is a current level, while for the FET a voltage is the controlling variable. In both cases, however, the controlled variable on the output side is a current level that also defines the important voltage levels of the output circuit.

The general relationships that can be applied to the analysis of all FET amplifiers are

$$I_G = 0 A$$

and  $I_D = I_S$

For JEETS and depletion type MOSFET's Shockley's equation is applied to relate the input and output quantities:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

For Enhancement MOSFET

$$I_D = k(V_{GS} - V_r)^2$$

It is particularly important to realize that of the equations above are for the device only. They do not change with each network configurations. So long as the device is in the actuve region.

**Table :** FET Bias Configurations

| Type/configuration/ pertinent equations         | Graphical solution                                                               |

|-------------------------------------------------|----------------------------------------------------------------------------------|

| JFET Fixed-bias $\gamma_{V_{DD}}$               | <b>↑</b> I <sub>D</sub>                                                          |

| R <sub>D</sub> R <sub>D</sub> V <sub>GG</sub> + | $\begin{array}{c c} I_{DSS} \\ \hline V_{P} & V_{GG} & 0 \\ V_{G}SO \end{array}$ |

| $\begin{split} I_{G} & \cong 0 \\ V_{GS} = \text{-} V_{GG} \\ V_{DS} & = V_{DD} \text{-} I_{D} R_{S} \end{split}$                                                            |                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| JFET self-bias $ \begin{array}{c} V_{DD} \\ R_{D} \\ R_{D} \end{array} $ $ \begin{array}{c} V_{GS} = -I_{D}R_{S} \\ V_{DS} = V_{DD} - I_{D} \\ (R_{D} + R_{S}) \end{array} $ | $V_{\text{P}} = -\frac{I_{\text{DSS}}/2}{2}$ $V_{\text{GS}} = -\frac{I_{\text{DSS}} \cdot R_{\text{S}}}{2}$ |

| JEFT/ Voltage-divider bias $R_1$ $R_2$ $R_3$ $V_{GS} = \frac{R_2 V_{DD}}{R_1 + R_2}$ $V_{GS} = V_{GS} - I_{D} R_{S}$ $V_{DS} = V_{DD} - I_{D}(R_D + R_S)$                    | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                        |

| JFET/common gate  VDD  RD  RS  -VSS                                                                                                                                          | Q-point [Vss/Rs]  VP 0 Vss Vgs                                                                              |

| $\begin{aligned} V_{GS} &= V_{SS}\text{-} I_D R_S \\ V_{DS} &= V_{DD} + V_{SS} \\ &= \text{-} I_D \left( R_D + R_S \right) \end{aligned}$ |                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| JFET ( $V_{GSQ} = 0 \text{ V}$ ) $V_{DD}$ $R_{D}$ $V_{GSQ} = 0 \text{ V}$ $I_{DQ} = I_{DSS}$                                              | $Q-point \bullet I_{DSS} \\ \bullet V_{GSQ} = 0V$ $V_{P}  0  V_{GS}$ |

| JFET $(R_D = 0\Omega)$ $Q$ $Q$ $Q$ $Q$ $Q$ $Q$ $Q$                                                                                        | Q-point I <sub>DSS</sub> $V_P V'_{GS} 0 V_{GS}$                      |

| Depletion type  MOSFET/ fixed-bias  VDD  RD  VGG  VGG  VGG  VDD  RD  VGS Q = + VGG  VDS = VDD - ID RS                                     | Q-point  V <sub>P</sub> 0 V <sub>GG</sub> V <sub>GS</sub>            |

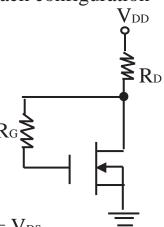

# Depletion-type

MOSFET/ voltage-divider bias

$$V_{G} = \frac{R_2 \; V_{DD}}{R_1 + R_2}$$

$$V_{\text{GS}} = V_{\text{G}} \text{ - } I_{\text{S}} \; R_{\text{S}}$$

$$V_{\text{DS}} = V_{\text{DD}} - I_{\text{D}} (R_{\text{D}} + R_{\text{S}})$$

# Enhancement type MOSFET/

feedback configuration

$$V_{\text{GS}} = V_{\text{DS}}$$

$$V_{\text{GS}} = V_{\text{DD}} \text{ - } I_{\text{D}} \ R_{\text{D}}$$

$$I_{\text{D}} = k[V_{\text{GS}} \text{ - } V_{\text{GS(tw)}}]^{\text{2}}$$

# Enhancement type MOSFET/ voltage

Divider bias  $R_1$   $R_2$   $R_3$   $R_5$

| 17      | $R_2 \; V_{\rm DD}$ |

|---------|---------------------|

| $V_G =$ | $R_1 + R_2$         |

$$V_{GS} = V_G - I_D R_S$$

Type/Symbol/ Basic relationships

# Transfer curve input resistance capacitance

# **JFET** (n-channel)

$$I_{C} = 0A$$

,  $I_{D} = I_{S}$   $D$

$$I_{DSS}$$

$$V_{P}$$

$$I_{D} = I_{DSS} \left(1 - \frac{V_{GS}}{V_{S}}\right)^{2}$$

$R_i > 100 M\Omega$  $C_i$ : (1 - 100) pF

# **MOSFET depletion-**

type (n-channel)

$$I_{D} = 0A, I_{D} = I_{S}$$

$$V_{DSS}$$

$$V_{P}$$

$$V_{DSS}$$

$$V_{P}$$

$R_i > 10^{10} \Omega$ C<sub>i</sub> (1 - 10) pF

# **MOSFET** enhancement type

$$k = \frac{I_{D \text{ (on)}}}{(V_{GS \text{ (on)}} - V_{GS \text{ (Th)}})^2}$$

$R_i > 10^{10} \Omega$  $C_i (1 - 10) pF$

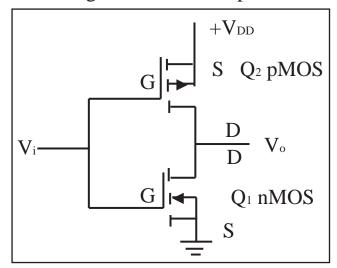

## **CMOS Biasing**

A form of circuit popular in digital circuitry uses both n-channel and p-channel enhancement MOSFET transistor. This complementary MOSFET or CMOS circuit uses these opposite (or complementary)-type transistors. The input, V<sub>i</sub> is applied to both gates with the output taken from the connected drains.

An input of 0V leaves the nMOS off, while an input of +5 V turns the nMOS on.

$V_{GS} = 0V$  leaves pMOS off :  $V_{GS} = -5V$  turns pMOS on.

| Operation of CMOS circuit |       |                |                        |

|---------------------------|-------|----------------|------------------------|

| V <sub>i</sub> (V)        | $Q_1$ | $\mathbb{Q}_2$ | $V_{o}\left( V\right)$ |

| 0                         | Off   | On             | +5                     |

| +5                        | On    | Off            | 0                      |

## **Diode Circuits**

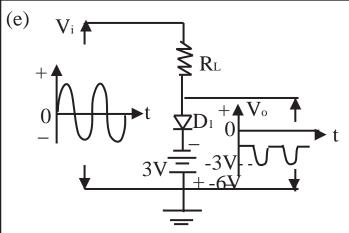

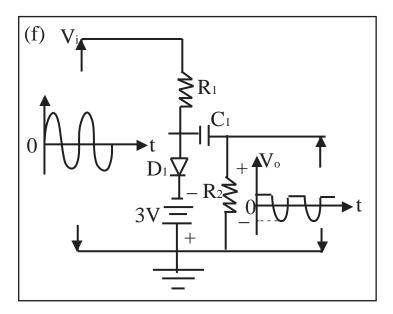

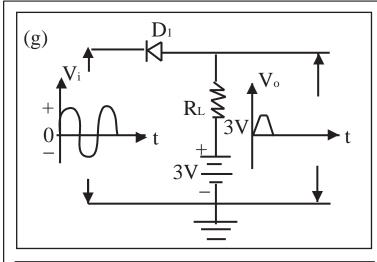

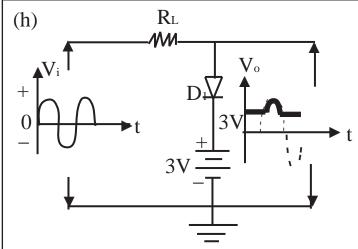

# **Diode Clipping Circuits**

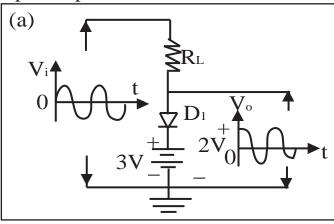

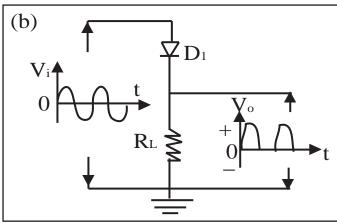

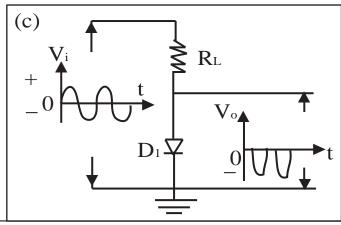

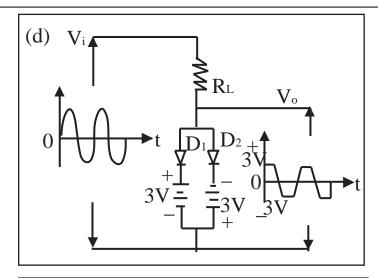

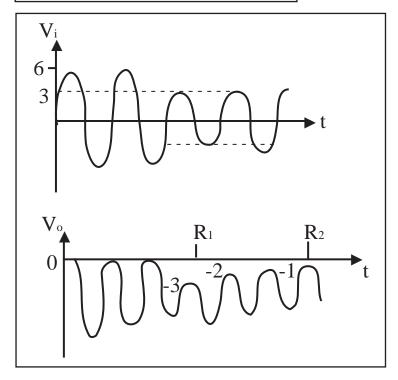

Clipping circuit are used to select for transmission that part of an arbitrary wave form which lies above or below some particular reference voltage level. These are also called voltage or current limiters. Some typical clipping with input output waveform are shown.

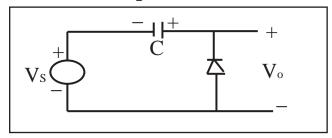

# **Diode Clamping Circuits**

The clamping circuit establisher a recurrent positive or negative extremity at some constant reference voltage level VR. The clamping circuit introduces a d.c component to a waveform that has lost its dc component after passing through a capacitive coupling network. For the reason, clamping circuit is often referred to as dc restorer or dc inverter.

In some situation it may be necessary to raise or lower reference voltage, which is done by adding or subtracting a dc voltage to the original reference voltage of 0.

# **Two Type of Clamper Circuit:**

- (a) If the d.c level added is positive, it is positive clamper.

- (b) If the d.c level is lowered and negative, it is negative clamper.

# **Negative Clamper**

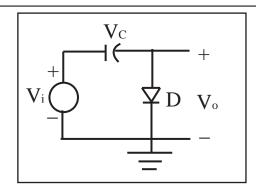

Consider the given circuit which consist of signal source  $V_i$  of neglecting output impedance a capacitor and diode D.

Assuming the ideal diode i.e  $V_y = 0$  and  $R_f = 0$ . The input is sinusoidal. During first quarter cycle of input signal the capacitor get charged as the diode is forward biased, no output voltage.

$$\therefore V_0 = 0$$

At the end of first quarter cycle  $V_c = V_m$ . After the diode comes reverse bias. The input signal reduces but the capacitor is not able to discharge due to diode.

$$V_o = V_i$$

-  $V_m$

During suceeding cycles the positive excusion of the signal just barely reaches zero. The diode need never again conduct and the positive extremity of the signal has been clamped or restore to zero.

If the amplitude of the input signal increases, the diode will conduct for first quarter cycle. The capacitor will again get charged and positive extremity will get clamped to zero voltage.

However, if the amplitude of input signal decrease. The signal does not remain clamped to zero. The reason being that capacitor does not get path to discharge.

To permit a decrease in capacitor voltage it is necessary to shunt a resistor across c or to shunt a resistor across the diode.

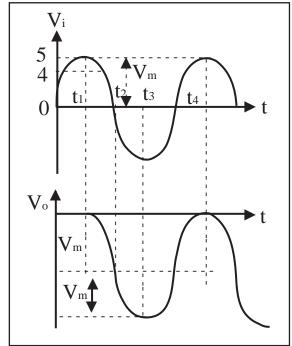

The circuit with shuntting diode is given below.

Now the capacitor get a discharge path. When the input suddenly rate.

$$V_o \equiv V_i \longrightarrow V_{ml}$$

Even if the input does not decrease to 3V the capactior continues to discharge and diode get forward bias during the peak of input voltage capacitor charge

during peaks. The RC time constant is very important. It must be very large in comparison with the period of signal. If it become if capacitorlosses too much of charge when diode is not conducting, then it may be that it does not charge during the small time interval when diode conduct.

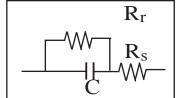

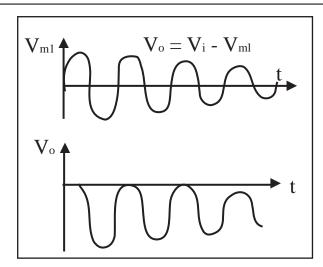

Clamping circuit taking source and diode resistance into account.

The realistic clamping circuit is given below:

Here source resistance Rs and diode forward resistance takes into account.

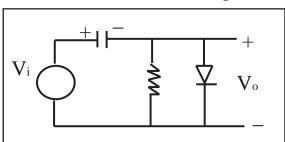

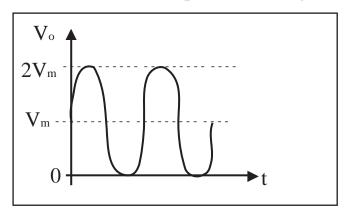

# **Positive Clamper**

$V_s = V_m$  sin wt, for negative swing D conducts and capacitor charge to peak value  $V_m$  and cathode end of capacitor is positive.

$$V_o = V_s + V_c \text{ (or } V_m)$$

= 2 Vm for positive swing and 0 for negative swing

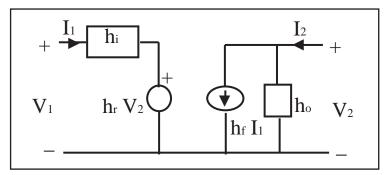

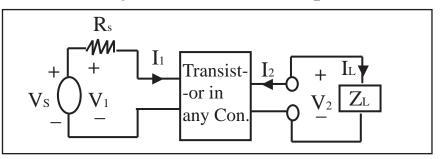

# Transistors at Low and High Frequencies Hybrid Model: H-Para meter Model

$$V_1 + V_2 + V_2$$

Transistor in any configuration

$V_1 + V_2$

$$V_1 = h_{11} I_1 + h_{12} V_2$$

$$I_2 = h_{21} I_1 + h_{22} V_2$$

$V_1$  and  $I_2 \rightarrow$  dependent Variable

$I_1$  and  $V_2 \rightarrow$  Independent Variable

$$\begin{pmatrix} V_1 \\ I_2 \end{pmatrix} = \begin{pmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{pmatrix} \begin{pmatrix} I_1 \\ V_2 \end{pmatrix}$$

$$h_i = h_{11} = \left. \frac{V_1}{I_1} \right|_{V_2 \, = \, 0}$$

Input impedance when output is short circuit  $(\Omega)$

$$h_r = h_{21} = \left. \frac{V_1}{V_2} \right|_{I_1 = 0}$$

Reverse voltage gain when input is open circuit.

h<sub>f</sub> = h<sub>21</sub> =

$$\frac{I_2}{I_1}$$

$V_2 = 0$

Forward current gain when output is short circuit.

$$h_o = h_{22} = \left. \frac{I_2}{V_2} \right|_{I_1 \, = \, 0}$$

Output admitance when input is open circuit (s).

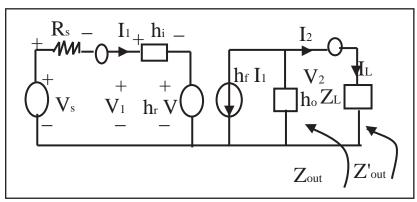

$$V_1 = h_i I_1 + h_r V_2 \leftarrow KVL$$

$$I_2 = h_f \, I_1 + h_o \, V_2 \longleftarrow KCL$$

# **Important Point of Hybrid Model**

- 1. We use h-parameter in the equivalent circuit of a transistor since this parameters are relatively constant (real number) with respect to audio frequency and temperature.

- 2. We find the h-parameter under different condition, i.e by open circuit the input or short circuit the output. Since these parameter have mixed units, these are called hybrid parameter.

- 3. For a given configuration of transistor the form h-parameter are always specified by manufactures.

- 4. They are easy to measure.

- 5. They can be obtained from the transistor ststic characteristic curves.

- 6. These are particularly convenient to use in the circuit analysis and design.

- 7. There parameter hold good for any configuration specified type of transistor

that in NPN or PNP, Si or Ge at low frequency.

#### **General Analysis of Transistor Amplifier**

$$V_1 = h_i I_1 + h_r V_2$$

$$I_2 = h_f I_1 + h_o V_2$$

Current gain (A<sub>1</sub>)

$$A_1 = \frac{I_L}{I_1} = \frac{-I_2}{I_1}$$

$$I_2 = h_f I_1 + h_o V_2$$

#### Divide the above equation by I1

$$\frac{I_2}{I_1} = h_f + h_o \left(\frac{V_2}{I_1}\right) \tag{1}$$

Now

$$V_2 = I_L Z_L = -I_2 Z_L$$

(2)

From equation (1) and (2)

$$\frac{I_2}{I_1} = h_f + h_o \left( \frac{-I_2 Z_L}{I_1} \right)$$

$$\frac{I_2}{I_1} (1 + h_0 Z_L) = h_f$$

$$\frac{I_2}{I_1} = \frac{h_\mathrm{f}}{1 + h_\mathrm{o} \; Z_\mathrm{L}}$$

$$A_{1} = -\frac{I_{2}}{I_{1}} = \frac{-h_{f}}{1 + h_{o} Z_{L}}$$

Input impedance (Zin )

$$Z_{in} = \lceil V_1 / I_1 \rceil$$

$$V_1 = h_i \; I_1 + h_r \; V_2$$

Divide the above equation by I<sub>1</sub>

$$\frac{V_1}{I_1} = h_i + h_r \frac{V_2}{I_1} = h_i + h_r \left(\frac{-I_2 Z_L}{I_1}\right)$$

Put the value of V<sub>2</sub> from equation (2)

$$Z_{in} = -h_i + h_r \cdot A_1 Z_L$$

Volatge gain (A<sub>v</sub>)

$$A_{v} = [V_{2}/V_{1}]$$

Put the value of equation (2)

$$V_1 = I_1 \; Z_{\rm in}$$

$$A_v = \frac{\text{-}I_2\;Z_L}{I_1\;Z_{in}} \quad ; \quad \ A_v = \frac{A_1\;Z_L}{Z_{in}} \label{eq:Av}$$

Output impedance Zout

$$Z_{\text{out}} = \frac{V_2}{I_2} \bigg|_{V_s = 0}$$

$I_2 = h_f I_1 + h_o V_2$

Divide the above equation by V<sub>2</sub>

$$\frac{I_2}{V_2} = h_f \frac{I_1}{V_2} + h_o \tag{3}$$

KVL at input:

$$-V_s + I_1 (R_s + h_i) + h_r V_2 = 0$$

$$0 + I_1(R_s + h_i) = -h_r V_2$$

$$\frac{I_1}{V_2} = \frac{-h_f}{R_s + h_i} \tag{4}$$

From equation (3) and (4)

$$\frac{I_2}{V_2} = h_{\rm f} \left( \frac{-h_{\rm f}}{R_{\rm s} + h_{\rm i}} \right) + h_{\rm o}$$

$$Z_{\text{out}} = \left[ h_{\text{o}} - \frac{h_{\text{f}} \; h_{\text{r}}}{(R_{\text{s}} + h_{\text{i}})} \right] \quad Z'_{\text{out}} = Z_{\text{out}} \mid\mid Z_{\text{L}}$$

Power gain  $A_P = A_v \cdot A_1$

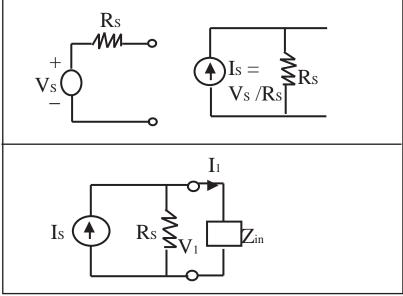

Voltage gain taking Rs into account i.e overall voltage gain

$$A_{vs} = \frac{V_2}{V_s} = \frac{V_2}{V_1} \times \frac{V_1}{V_s} = A_v \left(\frac{V_1}{V_s}\right)$$

$$\frac{V_1}{V_s} = \frac{Z_{in}}{Z_{in} + R_s}$$

$$A_{vs} = A_v \left[ \frac{Z_{in}}{Z_{in} + R_s} \right] = A_{vs} < A_v$$

$A_{vs} = A_v \Longrightarrow when R_s = 0$

Current gain taking Rs into account i.e overall current gain

$$A_{IS} = \frac{I_L}{I_S} = \frac{I_L}{I_1} \times \frac{I_1}{I_S} = A_1 \left(\frac{I_1}{I_S}\right)$$

$$\frac{\overline{I_1}}{I_s} = \frac{R_s}{R_s + Z_m}$$

$$A_{IS} = A_I \left[ \frac{R_s}{R_s + Z_{in}} \right] \quad A_{IS} < A_I$$

$A_{IS} = A_{I}$  when  $R_{S} = \infty$

=> Ideal current source

Overall power gain

$A_P = A_{VS} \times A_{IS}$

#### **Approximate Analysis of Transistor**

In general for a transistor if

1.

$$h_{oe} = 10^{-6} S$$

2.

$$h_{re} = 10^{-4}$$

3.

$$h_{oe} Z_L \le 0.1$$

Then it is seen that the error made in the analysis is < 10%, in such case approximate analysis hold good for CE.

$h_{re} = 10^{-4}$  neglected voltage source  $h_{rc}$   $V_{ce}$  is short circuit.

$h_{\text{oe}}=10^{\text{-6}}$

$S => (1/h_{oe})$  is large which draw negligible current i.e. open circuit.

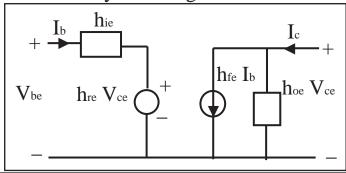

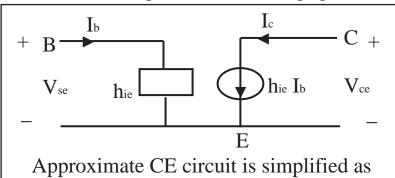

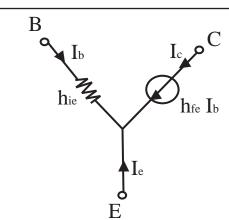

Approximate h-model which may be used for all three configuration

$$\begin{array}{l} h_{\rm re} = 10^{\text{-4}} & h_{\rm oe} = 10^{\text{-4}} \, S \\ h_{\rm fe} = 100 & h_{\rm re} = 2k \end{array}$$

1.

$$A_I = \frac{I_L}{I_b} = \frac{-I_C}{I_b} = \frac{-h_{\text{fe}} \; I_b}{I_b} = h_{\text{fe}} \; \text{phase inversion}$$

2.

$$Z_{in} = \frac{V_{be}}{I_b} = \frac{-h_{ie} \cdot I_b}{I_b} = h_{ie} \approx 1 \text{ k}\Omega$$

3.

$$A_v = \frac{A_1}{Z_{in}} Z_L = -h_{fe} \frac{Z_L}{h_{ie}}$$

4.  $Z_{out} = \infty$ ; due to idle current source  $Z'_{out} = Z_{out} \mid \mid Z_L = \infty \mid \mid Z_L = Z_L$

- 1. The current gain is high (hfe)

- 2. Voltage gain is high

- 3. Input and output current are out of phase by 180°.

- 4. The input and output voltage are out of phase by 180°.

- 5. Input impedance is medium.

- 6. Output impedance is medium.

- 7. Since volatge gain and current gain both are simultaneously high, this configuration is always used as an amplifier.

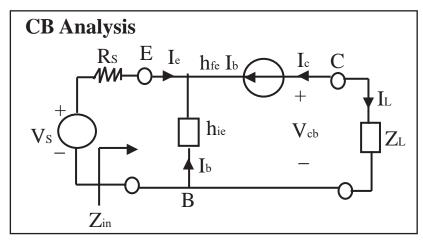

1. Current gain

$$\begin{split} A_{\rm I} &= \frac{I_{\rm L}}{I_{\rm e}} = \frac{-I_{\rm c}}{I_{\rm e}} \\ &= \frac{-h_{\rm fe}\;I_{\rm b}}{-(1+h_{\rm fe})I_{\rm b}} = \frac{h_{\rm fe}}{1+h_{\rm fe}} = \frac{\beta}{1+\beta} \; = < 1 \end{split}$$

2.

$$Z_{in} = \frac{V_{eb}}{I_e} = \frac{-h_{ie} I_b}{-(1 + h_{fe})I_b} = \frac{h_{ie}}{1 + h_{fe}} = \text{very low}$$

$$3. \ A_v = A_1 \, \frac{Z_L}{Z_{in}} = \left( \, \frac{h_{\rm fe}}{1 + h_{\rm fe}} \right) \times \frac{Z_L}{\left( \, \frac{h_{\rm ie}}{1 + h_{\rm fe}} \, \right)} = \frac{h_{\rm fe} \, . \, Z_L}{h_{\rm ie}}$$

4.

$$Z_{out} = \infty$$

$$Z_{out} = \infty \parallel Z_L = Z_L \Rightarrow \text{highest}$$

$$Z_{out} = \frac{V_{eb}}{I_c} \Big|_{V_s = 0} = \frac{V_{eb}}{0} = \infty$$

$$V_s = 0$$

;  $I_c = 0$

#### **Feature**

- 1. Low current gain ( $\alpha$ ) => always less than 1.

- 2. High voltage gain (approximately equal CE).

- 3. Input and output current are in phase.

- 4. Input and output voltage are in phase.

- 5. It has lowest input impedance of all three configurations.

- 6. It has highest output impedance of all three configurations.

- 7. Since, current gain is approximately equal 1, it can be used as constant current source.

- 8. Can be used at place where transformation of impedance from a very low value of very high value to desired.

- 9. Non-inverting amplifier with  $A_V > 1$  and  $A_I < 1$ .

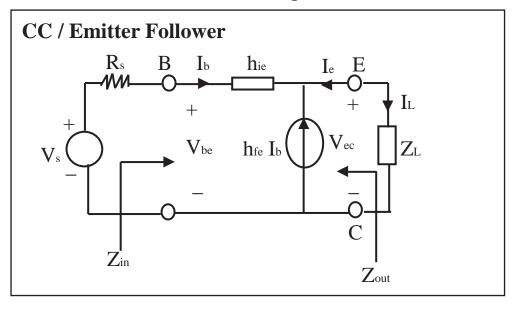

1.

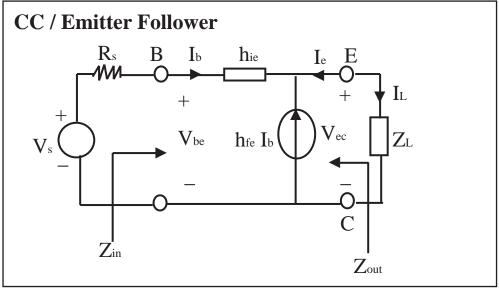

$$A_{I} = \frac{I_{L}}{I_{b}} = \frac{-I_{e}}{I_{b}} = \frac{(1 + h_{fe})I_{b}}{I_{b}} = 1 + h_{fe}$$

2.  $Z_{bc} = V_{bc}$  hie .  $I_{b} + I_{L} Z_{L}$

2.

$$Z_{in} = \frac{V_{bc}}{I_b} = \frac{h_{ie} \cdot I_b + I_L Z_L}{I_b}$$

=  $\frac{h_{ie} I_b + Z_L (1 + h_{fe})I_b}{I_b}$

$$Z_{in} = h_{ie} + (1 + h_{fe})Z_L \Longrightarrow highest$$

3.

$$A_v = A_I \frac{Z_L}{Z_{in}} = \frac{(1 + h_{fe})Z_L}{h_{ie} + (1 + h_{ef})Z_L} = \frac{x}{h_{ie} + x}$$

(<1)

where

$$x = (1 + h_{ef}) Z_L$$

$$\begin{aligned} 4. \ Z_{out} &= \frac{V_{ec}}{I_e} \bigg|_{V_s = 0} \\ V_{ec} &= -h_{ie} \ I_b - R_s \ I_b + V_s = -(h_{ie} + R_s) I_b \\ I_e &= -(1 + h_{fe}) I_b \\ Z_{out} &= \frac{h_{ie} + R_s}{(1 + h_{fe})} => lowest \end{aligned}$$

#### **Feature**

- 1. Highest current gain  $(1 + h_{fe})$ .

- 2. Voltage gain always less the unity (lowest).

- 3. Input and output current are in phase.

- 4. Input and output voltage are in phase.

- 5. Input impedance is the highest of all the three configurations.

- 6. Output impedance is the lowest of the three configurations.

7. Used at place where the impedance conversion from a high value to low value is desired. Therefore it is always used as last stage of any audio amplifier where its output impedance is matched to low impedance speaker to transfer maximum amount of power.

7. Used at place where the impedance conversion from a high value to low value is desired. Therefore it is always used as last stage of any audio amplifier where its output impedance is matched to low impedance speaker to transfer maximum amount of power.

- 8. Since it is having high input impedance therefore it can be used as a buffer amplifier, which draw negligible current and does not load the previous stage.

- 9. Zin depend upon the load.

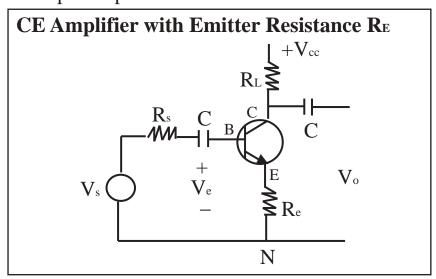

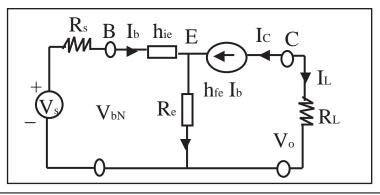

It is very important to stabilize the voltage amplification of an amplifier, i.e. it becomes independent or h-parameter.

$$I = I_b + h_{fe} I_b = (1 + h_{fe})I_b$$

2.

$$A_I = \frac{I_L}{I_b} = \frac{-h_{fe} I_b}{I_b} = -h_{fe} = > unaffected$$

$$3. \ Z_{in} = \frac{V_b}{I_b} = \frac{h_{ie} \ I_b + R_e \ I}{I_b}$$

$$= \frac{h_{ie} \ I_b + (1 + h_{fe})I_b \ . \ R_e}{I_b}$$

$$= h_{ie} + (1 + h_{fe})R_e$$

$Z_{in}$  increased by a factor of  $(1 + h_{fe}) R_e$

$$\begin{split} 4.~A_v &= A_I ~.~ \frac{Z_L}{Z_{in}} \\ &= \frac{-h_{\rm fe} ~.~ R_L}{h_{\rm ie} + (1+h_{\rm fe})R_e} => decreased \end{split}$$

5.

$$Z_{out} = \infty$$

$Z_{out} = \infty \mid \mid R_L = R_L$

#### **Comparison with Ce Amplifier**

- 1. The current gain and output impedance remain unchanged.

- 2. The input impedance is increased by the amount  $(1 + h_{fe})R_e$  ...... this is advantage.

- 3. The voltage gain decreased by the amount  $(1 + h_{fe})R_e$ .

$$\begin{split} A_v &= \frac{-h_{\rm fe} \cdot R_L}{h_{\rm ie} + (1+h_{\rm fe})R_e} \text{ as } h_{\rm fe} >> 1 \\ then &= \frac{-h_{\rm fe} \cdot R_L}{h_{\rm ie} + h_{\rm fe} \cdot R_e} = \frac{-h_{\rm fe} \cdot R_L}{h_{\rm fe} \cdot R_e} = \frac{-R_L}{R_e} \\ Let, h_{\rm fe} R_e >> h_{\rm ie} \quad \dots \quad practically \end{split}$$

$$A_v = -\frac{R_L}{R_e}$$

i.e. voltage gain is independent of h-parameter.

The h-parameter of transistor vary with respect to temperature so that the voltage gain changes with respect to temperature. Hence since the voltage gain is independent of h-parameter therefore the voltage gain is stabilized against the variation in temperature.

Therefore stability of the circuit increase.

# **Transistor Parameter value at Low Frequencies**

| Parameter           | CE                     | CC       | СВ                 |

|---------------------|------------------------|----------|--------------------|

| hi                  | $1.1~\mathrm{k}\Omega$ | 1.1ΚΩ    | $20\Omega$         |

| $h_{\rm r}$         | $2.5 \times 10^{-4}$   | 1        | $3 \times 10^{-4}$ |

| $h_{\mathrm{f}}$    | 50                     | -51-0.99 |                    |

| [1/h <sub>0</sub> ] | 40 kΩ                  | 40 kΩ    | 2 MΩ               |

Approximate values for different quantities using approximate equivalent model are given as follows:

|      | СВ                                           | CC                                                | CE                                           | CE with Re                                                 |

|------|----------------------------------------------|---------------------------------------------------|----------------------------------------------|------------------------------------------------------------|

| Aı   | $\frac{h_{\rm fe}}{1+h_{\rm fe}}$            | $1 + h_{\text{fe}}$                               | -h <sub>fe</sub>                             | -h <sub>fe</sub>                                           |

| Zin  | $\frac{h_{\text{ie}}}{1+h_{\text{fe}}}$      | $h_{\text{ie}} + (1 + h_{\text{fe}})R_{\text{L}}$ | hie                                          | $h_{\mathrm{ie}} + \ (1 + h_{\mathrm{fe}}) R_{\mathrm{e}}$ |

| Av   | $\frac{h_{\text{fe}} \; R_L}{h_{\text{ie}}}$ | $1 - rac{h_{	ext{ie}}}{Z_{	ext{in}}}$            | $\frac{-h_{\rm fe} \ R_{\rm L}}{h_{\rm ie}}$ | $\frac{-h_{\rm fe} \ R_{\rm L}}{Z_{\rm in}}$               |

| Zout | $\infty$                                     | $\frac{R_s + h_{ie}}{1 + h_{fe}}$                 | 8                                            | $\infty$                                                   |

| Zout | $R_{\rm L}$                                  | Zout     RL                                       | $R_{\rm L}$                                  | R <sub>L</sub>                                             |

#### **Amplifiers**

## **Power Amplifier**

Power Amplifier are meant for large signal amplification power stage is normally the final stageof a cascade amplifier and driver. The energy conversion device i.e., speaker, antenna or transducer etc. The power amplifier does not actually amplify the power, instead it takes power from the dc power supply connected to the power circuit and converts into use full ac signal power  $Z_{in} \rightarrow high$ ,  $Z_{out} \rightarrow low$ , heat sink are used.

#### Class A

Here the dc bias is adjusted much less than its cut off value so that output current flow for full input voltage cycle.

#### Feature:

- 1. Minimum distortion.

- 2. Since the output contains only one frequency component, the output power is small.

- 3. Effeciency is low.

- 4. Used as voltage amplifier as modulating amplifier.

#### Class B

Here the dc bias is adjusted equal to the cut off value so that the output current flow foe half of the input voltage cycle. Hence the output dc component will be always equal to zero.

#### Feature:

- 1. High distortion.

- 2. High power output

- 3. Effeciency is large

- 4. Used as power amplifier as modulated amplifier.

#### Class AB

Here the dc bias is adjusted slightly less than cut-off value so that the output current flows for more than half but less than input voltage cycle. This class of amplifier is just a compromise between class A and class B amplifier.

#### Feature:

- 1. Output power is medium.

- 2. Medium distortion.

- 3. Medium effeciency.

- 4. Used as modulating amplifier

- 5. used with unturned power amplifier.

#### Class C

Here the dc bias is adjusted greater than its cut-off value so that the output current flow for less than half of the input voltage cycle.

Therefore the output current will be in the form of pulses which will be highly rich in ahrmonic i.e frequency multiplier.

#### Feature:

- 1. Very high output power due to reach in harmonic.

- 2. Very high distortion.

- 3. Very high conversion efficiency.

- 4. Used as only modulated amplifier when the need is to raise the power level before transmission.

- 5. Used with tuned frequency amplifier.

| Power Amplifier            |                            |                               |  |  |

|----------------------------|----------------------------|-------------------------------|--|--|

| ▼<br>Singled Ended         | Transformer                | Push Pull                     |  |  |

| Class A                    | Class A                    | Class AB                      |  |  |

| $\eta_{\text{max}} = 25\%$ | $\eta_{\text{max}} = 50\%$ | $\eta_{\text{max}} = 78.50\%$ |  |  |

## **Single Ended Class A Amplifier**

#### **Class A transformer Coupled**

Conversion efficiency  $(\eta)$

$= \frac{\text{Signal power delivered to load}}{\text{DC power supplied to output circuit}} \times 100 = 50\%$ [DC power supplied (Vcc Ic)]

= AC power developed in load  $\left(\frac{1}{2}V_{m} I_{m}\right)$

+ power dissipated in load R<sub>L</sub>(I<sub>c</sub><sup>2</sup> R<sub>L</sub>)

+ Dissipation in the Collector PD

With no signal  $P_D$  (max) =  $V_{CE}$ .  $I_C$

$\therefore$  P<sub>ac</sub> delivered =  $\frac{1}{2}$  P<sub>D</sub> max

This statement is true in both series fed and Transformer coupled cases.

Given  $P_D$  max = 20 watts

Then in series fed  $P_{ac}$  to load = 10 watts

$P_{dc} = 40$  watts  $(\eta = 25\%)$

In transformer coupling with  $P_D$  max = 20 watts

$$P_D = 20 \text{ watts } (\eta = 50\%)$$

Since only 25% ac power is useful at the power output.

$$\eta_{max} = 25\%$$

- 1. Effeciency is very low. This is become of the fact in the large amount of dc power is dissipated across the load.

- 2. The effeciency can be increased to 50% in transformer where  $R_L$  is effectively isolated from the power supply  $V_{CC}$  using the transformer coupling as shown.

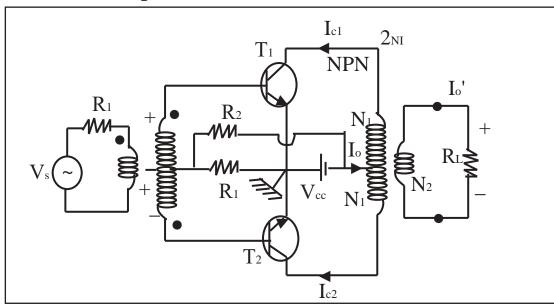

#### **Push - Pull Amplifier**

$$R_L' = \left(\frac{2N_1}{N_2}\right)^2 R_L$$

Output load current =  $k(i_{c1} - i_{c2})$

$= 2k(B_1 \cos \omega t + B_1 \cos 3\omega t + ....)$

Only odd harmonics are present. The push pull system has balanced out the even harmonics.

→ In class B operation, the operating point is at cut-off so that signal is amplified by one transistor only for one half of the cycle,

$$\eta = \frac{P_{ac} \text{ to load}}{P_{dc}} = \frac{\pi}{4} \left( \frac{V_{cc} - V_{min}}{V_{cc}} \right) \times 100$$

Theoretical max.  $\eta = max = \pi/4 \times 100 = 78.5\%$

Also

$$\frac{P_{Dmax}}{P_{ac max}} = \frac{4}{\pi^2} = 0.4$$

Under these maximum values of  $P_{ac}$ ,  $P_D$  per transistor = 0.2  $P_{ac}$ ,  $P_D$  max =  $\frac{1}{5}$   $P_{ac}$  max

Maximum AC power obtained in class B push pull = 5 P<sub>D</sub> (of the transistor).

#### Characteristic:

- 1. The ven harmonic are absent at the output of a push-pull amplifier i.e  $I_C = 2I_1 \sin \omega t + 2 I_2 \sin 3\omega t + ...$

- 2. The amplifier gives more output power per transistor for a given amount of distortion.

- 3. Less distortion is achieved for a given power output per transistor.

- 4. The dc components of the output current of the two transistor oppose each other in the transformer. This eliminates the tendency of the output core of the transformer to saturate. Therefore, the losses in the transformer are minimized.

- 5. The effect of ripple voltage contained in the power supply are just balanced out since the current produced are in the opposite direction.

- 6. Due to non saturation of core the transformer contains less ferromagnetic material.

- 7. The output transformer for push pull amplifier circuit are lighter, smaller and less expensive than the transformer of comparable quality used in single ended transform amplifier.

# **Multistage Amplifier Cascaded Amplifier**

- Gain of one stage of amplifier may not be sufficient to obtain the required gain may be worked out in a single stage, the operating condition of the transistors may be impracticable.

- Overall gain is the product of gain of individual stages.

- $A_{VT} = A_{V1} \times A_{V2}$

#### **Frequency Response of Cascaded Stages**

For n identical stages:

- 1. The upper cut-off frequency decreases  $f_H = f_H \sqrt{(2^{1/n} 1)}$

- 2. The lower cut off frequency increase

$$f_{L} = \frac{f_{L}}{\sqrt{2^{1/n} - 1}}$$

- 3. Overall bandwidth decrease.

- 4. The gain bandwidth product remain constant.

5. The Transmission line parameter are used, i.e. A, B, C, D.

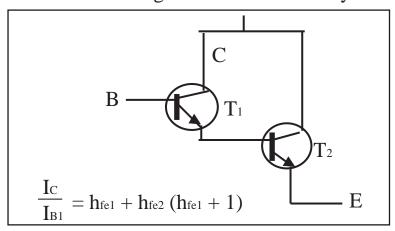

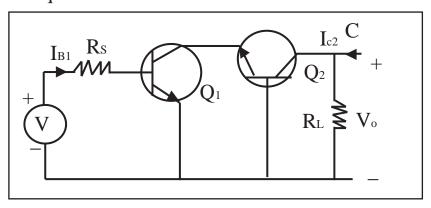

#### **CC - CC (Darlington Pair)**

The CC amplifier has high input impedance as a single transistor to increase the input impedance still further we use the Darlington emitter follower, which is CC-CC amplifier. The two transistors form a composite pair. this can be considered as single transistor with only three external lead.

Assuming two transistor is having same hee

$$\frac{I_C}{I_{B1}} = h_{fe} \times h_{fe} = h^2_{fe}$$

;  $A_v \approx 1$

#### **Input Impedance**

$R_{\mathrm{i}} = h_{\mathrm{ie1}} + (h_{\mathrm{fe1}} + 1) \; h_{\mathrm{ie2}} \label{eq:Riemann}$

$R_i = 2h_{ie2} \left( h_{fe1} + 1 \right)$

Assuming  $h_{ie1} = h_{ie2} = h_{ie}$

#### **Cascode Connection**

This CE - CB connection

- Common emitter stage drives a common base amplifier.

- Gain can be improved by using large value of R<sub>L</sub> over a wide range of frequencies.

- Overall current gain  $A_I \frac{I_{C2}}{I_{B2}} = \beta_0$

- Voltage gain =  $A_v = \frac{-\beta_0 R_L}{(R_s + r_{be})}$

- Output resistance of a CB stage is high, so we can connect a large load resistance R<sub>L</sub>.

- This input resistance for the CB stage is low and this is the load resistance for the CE stage. The low input resistance of CB stage makes Q<sub>1</sub> operate into a short-circuit load, so voltage gain of common emitters stage is low. This cause reduces the input capacities so its Bandwidth gets increased.

- It is used in wide Band amplifiers due to its large bandwidth.

#### **Tuned Amplifier**

To provide gain at particular frequency tuned circuit are used at the input and output terminal. It is operated on RF frequency. The effective Q of the resonant circuit be high enough so the V<sub>o</sub> consist only the direct voltage and fundamental component of signal i.e. of to eliminate the harmonics.

Function of the resonant circuit are:

- 1. To provide the correct load impedance.

- 2. To reject the unwanted harmonic.

- 3. To couple the power to the load.

#### **Differential Amplifier**

It is the basic building block of the operational amplifier:

- The first stage of an op-amp is Differential amplifier (DA).

- DA consists of two transistor which are emitter coupled and whole characteristic are identical.

There are two type of input signal to the DA:

Differential mode :  $V_d = V_1 - V_2$

Common mode : It is the average between the input voltage  $V_2$  and  $V_1$

$$V_c = \frac{V_1 + V_2}{2}$$

High frequency Analysis

$$A_{\text{DM}} = \frac{-h_{\text{fe}} \cdot R_{\text{L}}}{R_{\text{s}} + r_{\text{b'b}} + r_{\text{b'e}}} = \frac{-h_{\text{fe}} \cdot R_{\text{L}}}{r_{\text{b'e}}} = -g_{\text{m}} R_{\text{L}}$$

$$A_{\text{CM}} = \frac{-g_{\text{m}} \cdot R_{\text{L}}}{1 + 2 \ g_{\text{m}} \ R_{\text{E}}}$$

Low frequency analysis

$$A_{\text{d}} = \frac{-h_{\text{fe}} \; . \; R_{\text{o}} \; R_{\text{L}}}{h_{\text{ie}} \; (R_{\text{o}} + 2R_{\text{L}})} \label{eq:Ad}$$

$$A_c = \frac{-h_{\rm fe} \cdot R_L}{h_{\rm ie} + 2(1 + h_{\rm fe})R_e}$$

Where ADM and ACM is known as differential mode gain and common mode gain.

## Common mode rejection ration (CMRR)

$$\bullet \ CMRR = \frac{A_{DM}}{A_{CM}}$$

- CMRR =  $1 + 2g_m R_E \approx 2 g_m$ . RE

- For large value of CMRR, we need large value of RE, so use current source having high output resistance for FET based differential amplifiers.

• CMRR =

$$\frac{1 + 2 R_s \mu}{r_d} \approx 2g_m R_s$$

#### **Feedback Amplifier Topologies**

There are four basic type:

1. Shunt-Shunt

2. Shunt-Series

3. Series-Shunt

4. Series-Series

These designation corresponds to the input and output port connection respectively between the feedback network and the basic amplifier.

Gain with feedback

$$A_{\rm f} = \frac{X_{\rm o}}{X_{\rm s}} = \frac{A}{1 - \beta. A}$$

Where A = transfer function without feedback.

If  $|A_f| \le |A|$ , the feedback is termed as negative.

And if  $|A_f| > |A|$ , the feedback is termed as positive.

#### **Fundamental Assumption**

Three conditions are implicit in the representation of the ideal feedback amplifier.

- 1. The input signal is transmitted to the output through the amplifier A and not through the feedback networ  $\beta$ . Means feedback network is unilateral.

- 2. The feedback signal is transmitted from output to input through the feedback network only.

- 3. The transfer ratio  $\beta$  is independent of source and load resistance.

## **Property of Negative-Feedback Amplifiers**

Although negative feedback results in reduced gain, it is used because of following reasons:

- Bandwidth get increased.

- Effect of noise get reduced

- Distortion get reduced.

#### **Input Impedance in Feedback Amplifier Input Resistance**

If the feedback signal is returned to the input in series with the applied voltage, the input impedance get increased.

$$R_{if} = R_i (1 - \beta A)$$

Where,  $R_{if}$  = Input resistance after feedback

$R_i$  = Input resistance without feedback.

• For negative feedback  $V_f$  is  $180^\circ$  out of phase with  $V_s$ ,  $V_i$  is less than it would be if  $V_f$  were absent. Hence  $I = V_i / R_i$  decreased.

Causes the ratio V<sub>s</sub> /I to increase.

• If shunt connection is used at the input of a negative feedback amplifier, the impedance decreases.

$$R_{if} = \frac{R_i}{(1 - \beta . A)}$$

#### **Output Impedance**

When the output of a feedback employs a shunt connection, negative feedback reduces the Output resistance .

$$R_{\rm of} = \frac{R_{\rm o}}{(1 - \beta . A)}$$

Output impedances increased when a negative feedback amplifier employs a series connected output.

$$R_{Of=Ro} (1 - \beta.A)$$

Effect of feedback on Bandwidth

Open loop gain

$$A_{OL} = \frac{A_o}{1 + \left(\frac{S}{\omega_n}\right)}$$

(without feedback)

#### Return Ratio

$$T(s) = \frac{T_o}{\left[1 + \left(\frac{S}{\omega_n}\right)\right]}$$

Where  $A_0$  and  $T_0$  are the midband value of  $A_{OL}$  and T(s),  $\omega_n$  is angular frequency of the dominant pole.

$$A(s) = \frac{A_{OL}}{1 + A_{OL} \cdot T(s)} = \frac{A_{FO}}{\left[1 + \left(\frac{S}{\omega_{P}}\right)\right]}$$

where,

$$A_{FO} = \frac{A}{(1 + T_o)}$$

$$\omega_H = (1 + T_o) \omega_n$$

Negative feedback has increased the bandwidth by a factor  $(1 + T_0)$ , the same factor by which  $A_{OL}$  is reduced.

#### **Stability**

In the design of a feedback amplifier, it must be ascertained that the circuit is stable at all frequencies.

A system is stable if and only if all bounded input signal produce bounded output signals

• If a pole of transfer function exists with a positive real part, this cause output to increase exponentially with time and hence unbounded.

#### **Stability of Feedback Amplifiers**

$$A_{i}(s) = \frac{A_{OL}(s)}{1 + T(s)}$$

Amplifier without feedback is stable if all the pole of AoL lie in the left half of s-plane.

Amplifier with feedback is stable if all the zero of T(s) lie in the left half of s-plane.

#### **Feedback Amplifier Configuration**

Feedback is the process whereby a portion of the output is returned to the input to form part of the system excitation.

Feedback was used to make the operating point of a transistor insensitive to both manufacturing variation in  $\beta_1$  and temperature.

Effect of negative feedback on amplifier characteristic

| Type of feedback |              |                 |                            |                 |  |  |

|------------------|--------------|-----------------|----------------------------|-----------------|--|--|

|                  | Volatage     | Current         | Current                    | Volatge         |  |  |

|                  | series       | series          | shunt                      | shunt           |  |  |

| Zout             | Decrease     | Increases       | Increases                  | Decreases       |  |  |

| Zin              | Increases    | Increases       | Decreases                  | Decreases       |  |  |

| Improves         | Volatge      | Transconduct-   | Current                    | Trans-          |  |  |

| characteristics  | Amplifier    | -ance amplifier | Amplifier                  | Resistance      |  |  |

| of               |              |                 |                            | amplifier       |  |  |

| Desensitizes     | $A_{\rm vf}$ | $G_{ m Mf}$     | $\mathbf{A}_{\mathrm{if}}$ | R <sub>MI</sub> |  |  |

## **Type of Feedback Amplifiers**

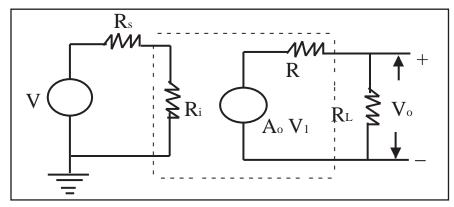

# Voltage Amplifier Or Voltage Series Amplifier

$$R_i >> R_s$$

;  $R_o << R_L$

$R_i$  = Input resistance of the amplifier

This circuit provides an output voltage proportional to the input voltage.  $R_i >> R_s$  and  $R_o >> R_L$ .

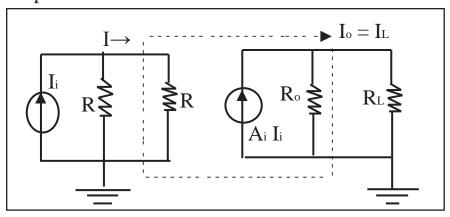

## The current Amplifier or Current Shunt Amplifier

An ideal current-controlled source has zero input resistance  $R_i$  and has infinite output resistance  $R_o$ .

$\mid R_i \mid << R_s \text{ and } \mid R_o \mid >> R_L \text{ ; } I_o = A_i \; I_i$

Output current is proportional to input current.

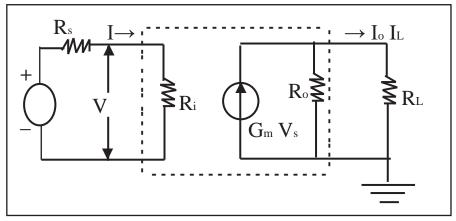

# The Voltage-Current Converter or trans-conductance Amplifier (Voltage Controlled current source) or Current Series Amplifie

This ideal voltage - controlled current source.

$|R_i| >> R_s$  and  $|R_o| >> R_L$

$I_o = G_m V_s$

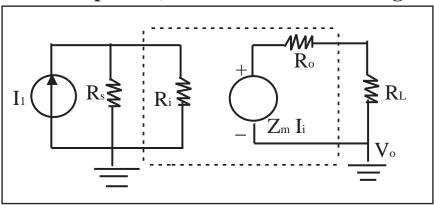

# **Current-voltage Converter or Trans-Impedance Amplifier or Voltage Shunt Amplifier (Current Controlled Voltage Source)**

This is ideal current controlled voltage source

$R_i >> R_s$  and  $\mid R_o \mid << R_L$

$V_{\text{o}} = Z_{\text{m}} \; I_{\text{s}}$

## **Operational Amplifier**

1st Stage : Difference amplifier

2nd Stage: High gain linear amplifier

3rd Stage: Emitter follower.

4th Stage: DC level shifter and output amplifier

## **Ideal Op-amp Characteristics**

- 1. Input resistance is infinite,  $Z_{\text{in}=\infty}$ , so no current enters the input terminal.

- 2. A zero output resistance,  $Z_{out} = 0$

- 3. Infinite voltage gain,  $A_v = \infty$

- 4. Characteristics do not drift with temperature.

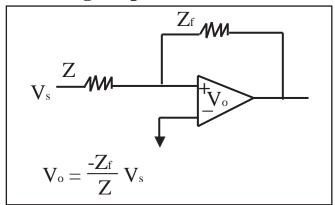

# **Application of OPS Amplifier Inverting Amplifier**

Input Impedance: The input resistance is equal to resistance Z.

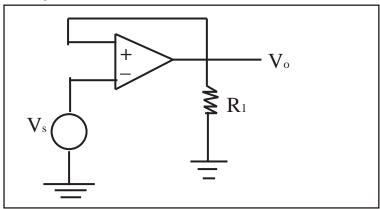

## **Unity Follower**

The output signal is in phase with the input signal and of same magnitude. Input impedance is very high, so it provides very good isolation between stages.

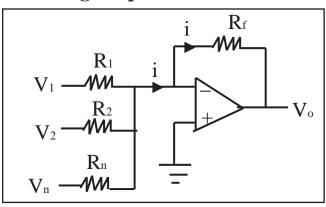

## **Summing Amplifier**

$$V_{o} = -\left(\!\frac{R_{\rm f}\,V_{1}}{R_{1}} + \,\frac{R_{\rm f}\,V_{2}}{R_{2}} + \frac{R_{\rm f}\,V_{n}}{R_{n}}\!\right)$$

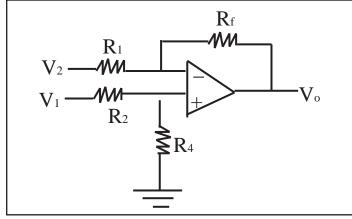

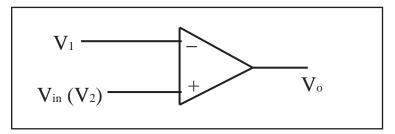

# Differential Amplifier

If

$$\frac{R_2}{R_1} = \frac{R_4}{R_3}$$

;  $V_0 = \frac{R_f}{R_1} [V_1 - V_2]$

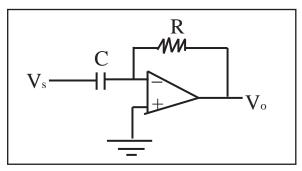

## **Differentiator**

$$\frac{V_{o}\left(s\right)}{V_{s}\left(s\right)}=-sRC$$

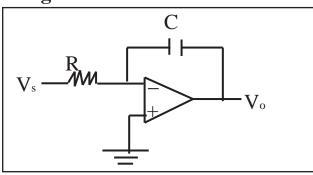

# **Integrator**

$$\frac{V_{o}(s)}{V_{s}(s)} = \frac{1}{sRC}$$

## **All Pass Filter**

$$\frac{V_o}{V_i} = \frac{1 - j\omega \ RC}{1 + j\omega \ RC} = \frac{1 - sRC}{1 + sRC}$$

$|H(j\omega)| = 1$  and phase shift =  $2 \tan^{-1} (\omega RC)$

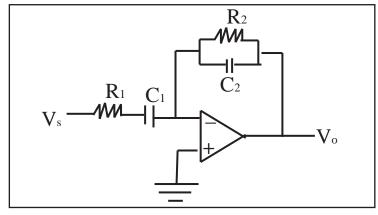

#### **Band Pass Filter**

$$\frac{V_o}{V_s} = \frac{-sC_1 R_2}{(1 + sC_2 R_2)(1 + sC_1 R_1)}$$

#### **Type of Filter**

Putting  $\omega = 0$  (capacitor open-circuit) and  $\omega = \infty$  (capacitor short-circuited)

In above circuit when  $\omega = 0$ ,  $C_1 =$  open circuit and  $V_0 = 0V$ , similar for  $\omega = \infty$   $(C_1 = C_2)$  so it does not pass high as well as low frequency so it is band pass.

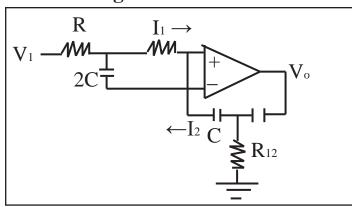

# **Non-Inverting Integration**

$$V_o = \frac{1}{RC} \int V_s \, dt$$

## **Double Integration**

$$\frac{V_o}{V_s} = - \frac{1}{(sRC)^2}$$

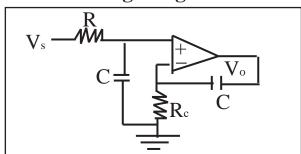

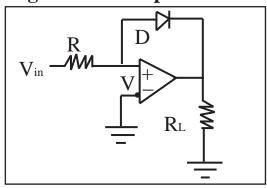

#### Logarithmic Amplifier

When  $V_{in} < 0$ ; diode is off, Op-amp behaves as comparator. At this time  $V_o = + V_{sat}$

- When  $V_{in} > 0$  diode is ON  $V_o = -0.7 \text{ V}$

- For small range V<sub>in</sub> . It behaves as logrithmic amplifier

$$V_o = 2.3 \frac{KT}{q} log_{10} \left( \frac{V_{in}}{R_L I_o} \right)$$

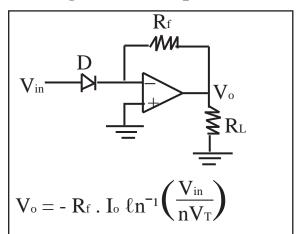

#### **Antilogrithmic Amplifier**

## **Comparator**

In a comparator, the level of the applied input voltage is compared with a known reference voltage :

- 1. As a comparator, the level of the applied input voltage is compared with a known reference voltage.

- 2. As a comparator, the Op-amp are operated in the open loop condition without feedback resistor.

- 3. Since it is operated in open loop condition, the assumption (V+ V- =  $V_d$  = 0) is not applicable.

- 4. Open loop gain is very high, so output goes to saturation levels ( $\pm\,V_{cc}$ )

even for very low inputs.

5. If 1 or 2V drops in  $R_c$ 's of the transistor of the differential stage, the saturation voltage will be  $(\pm 13 \text{ V})$  for a supply voltage of  $(\pm 15 \text{ V})$ .

$$\begin{split} &If~(V_2 \text{ - } V_1) = V_{in} > 0~,~V_o~= +~V_{sat}\\ &If~(V_2 \text{ - } V_1) = V_{in} < 0~,~V_o = \text{ - }V_{sat} \end{split}$$